Прерывания от внешних устройств в системе x86. Часть 1. Эволюция контроллеров прерываний

В данной статье хотелось бы рассмотреть механизмы доставки прерываний от внешних устройств в системе x86 и попытаться ответить на вопросы:

- что такое PIC и для чего он нужен?

- что такое APIC и для чего он нужен? Для чего нужны LAPIC и I/O APIC?

- в чём отличия APIC, xAPIC и x2APIC?

- что такое MSI? В чём отличия MSI и MSI-X?

- как с этим связаны таблицы $PIR, MPtable, ACPI?

Введение

Все мы знаем, что такое прерывание. Для тех, кто нет, цитата из википедии:

Прерывание (англ. interrupt) — сигнал от программного или аппаратного обеспечения, сообщающий процессору о наступлении какого-либо события, требующего немедленного внимания. Прерывание извещает процессор о наступлении высокоприоритетного события, требующего прерывания текущего кода, выполняемого процессором. Процессор отвечает приостановкой своей текущей активности, сохраняя свое состояние и выполняя функцию, называемую обработчиком прерывания (или программой обработки прерывания), которая реагирует на событие и обслуживает его, после чего возвращает управление в прерванный код.

В зависимости от источника возникновения сигнала прерывания делятся на:

- асинхронные, или внешние (аппаратные) — события, которые исходят от внешних аппаратных устройств (например, периферийных устройств) и могут произойти в любой произвольный момент: сигнал от таймера, сетевой карты или дискового накопителя, нажатие клавиш клавиатуры, движение мыши. Факт возникновения в системе такого прерывания трактуется как запрос на прерывание (англ. Interrupt request, IRQ) — устройства сообщают, что они требуют внимания со стороны ОС;

- синхронные, или внутренние — события в самом процессоре как результат нарушения каких-то условий при исполнении машинного кода: деление на ноль или переполнение стека, обращение к недопустимым адресам памяти или недопустимый код операции;

В данной статье хотелось бы обсудить внешние прерывания IRQ.

Зачем они нужны? Допустим мы хотим выполнить какое-либо действие со входным пакетом для сетевой карты, когда он придёт. Чтобы не спрашивать сетевую карту постоянно «есть ли у тебя новый пакет?» и не тратить на это ресурсы процессора, можно использовать прерывание IRQ. Линия прерываний устройства соединяется с линией INTR процессора, и при получении пакета сетевая карта «дергает» эту линию. Процессор понимает, что для него есть информация и читает пакет.

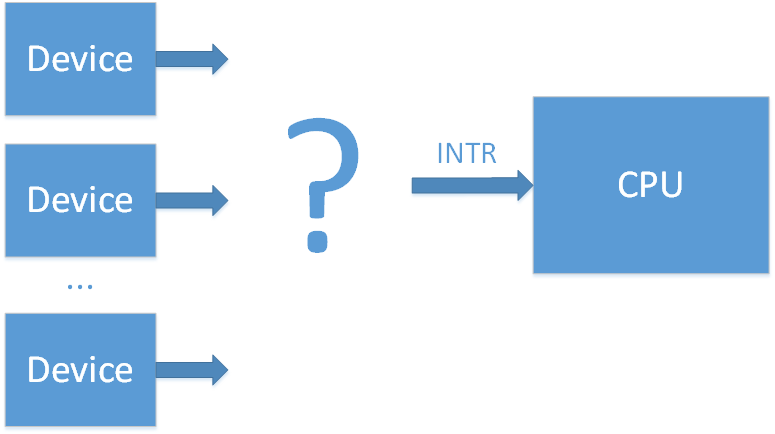

Но что делать если устройств много? На все внешние устройства ножек процессора не напасёшься.

Чтобы решить эту проблему, придумали микросхему — контроллер прерываний.

PIC

Первой была микросхема Intel 8259 PIC. 8 входных линий (IRQ0-7), и одна выходная, соединяющая контроллер с линией INTR процессора. Когда возникает прерывание от какого-либо устройства, 8259 дёргает линию INTR, процессор понимает, что какое-то устройство сигнализирует о прерывании и опрашивает PIC, чтобы понять по какой именно ножке IRQx возникло прерывание. Появляется дополнительная задержка на данный опрос, но зато количество линий прерываний увеличивается до 8.

Однако 8 линий быстро оказалось мало, и чтобы увеличить их количество стали использовать 2 контроллера 8259 (master и slave) соединённых каскадно (Dual PIC).

IRQ с 0 по 7 обрабатываются первым Intel 8259 PIC (master), а IRQ с 8 по 15 вторым 8259 PIC (slave). О возникновении прерывания CPU сигнализирует только master. Если возникло прерывание на линиях 8-15, второй PIC (slave) сигнализирует о прерывании мастеру по линии IRQ 2, и тот уже в свою очередь сигнализирует CPU. Это каскадное прерывание отнимает одну из 16 линий, но в итоге даёт 15 доступных прерываний для устройств.

Схема утвердилась, и именно её имеют ввиду, когда говорят сейчас о PIC (Programm Interrupt Controller). Впоследствии контроллеры 8259 получили некоторые улучшения, и стали называться 8259A, а эта схема вошла в состав чипсета. Во времена когда основной шиной для подключения внешних устройств была шина ISA, такой системы в целом хватало. Надо было лишь следить, чтобы разные устройства не подключались на одну линию IRQ для избежания конфликтов, так как прерывания ISA не разделяемые.

Обычно раскладка прерываний под устройства была более менее стандартная

Пример (взят отсюда):

IRQ 0 — system timer

IRQ 1 — keyboard controller

IRQ 2 — cascade (прерывание от slave контроллера)

IRQ 3 — serial port COM2

IRQ 4 — serial port COM1

IRQ 5 — parallel port 2 and 3 or sound card

IRQ 6 — floppy controller

IRQ 7 — parallel port 1

IRQ 8 — RTC timer

IRQ 9 — ACPI

IRQ 10 — open/SCSI/NIC

IRQ 11 — open/SCSI/NIC

IRQ 12 — mouse controller

IRQ 13 — math co-processor

IRQ 14 — ATA channel 1

IRQ 15 — ATA channel 2

Конфигурация и работа с микросхемами 8259 осуществляется через I/O порты:

| Чип | Регистр | I/O port |

|---|---|---|

| Master PIC | Command | 0x0020 |

| Master PIC | Data | 0x0021 |

| Slave PIC | Command | 0x00A0 |

| Slave PIC | Data | 0x00A1 |

→Документацию на 8259A можно найти тут

На смену шине ISA пришла шина PCI. И количество устройств явно стало превосходить число 15, плюс в отличие от статической шины ISA в данном случае случае устройства могут добавляться в систему динамически. Но к счастью в данной шине прерывания могут быть разделяемыми (то есть к одной линии IRQ можно подсоединить несколько устройств). В итоге чтобы решить проблему нехватки линий IRQ, прерывания ото всех PCI устройств решили группировать в линии PIRQ (Programmable Interrupt Request).

Допустим у нас 4 линии прерываний свободно на PIC контроллере, а PCI устройств 20 штук. Мы объединяем прерывания по 5 устройств на линию PIRQx и подключаем линии PIRQx к контроллеру. При возникновении прерывания на линии PIRQx процессору придётся опросить все устройства подключённые к данной линии, чтобы понять от кого именно пришло прерывание, но в целом это решает задачу. Устройство осуществляющее связывание линий прерываний PCI в линии PIRQ часто называют PIR router.

В данном методе надо следить, чтобы линии PIRQx не подсоединялись к линиям IRQx на которых уже заведены прерывания ISA (так как это вызовет конфликты), и чтобы линии PIRQx были сбалансированы (ведь чем больше устройств мы подключили к одной линии PIRQ, тем больше устройств надо будет опрашивать процессору, чтобы понять, какое именно из этих устройств вызвало прерывание).

Замечание: на рисунке маппинг PCI device -> PIR изображён абстрактно, потому что на самом деле он несколько сложнее. В реальности каждый PCI device имеет 4 линии прерываний (INTA, INTB, INTC, INTD). У каждого PCI устройства (device) может быть до 8 функций (functions) и вот каждой функции соответствует уже одно прерывание INTx. Какую именно INTx будет дёргать каждая функция устройства определяется конфигурацией чипсета.

По сути функции это отдельные логические блоки. Например в одном PCI устройстве может быть функция Smbus controller, функция SATA controller, функция LPC bridge. Со стороны ОС каждая функция — это как отдельное устройство со своим конфигурационным пространством PCI Config.

Информацию о роутинге прерываний на PIC контроллере BIOS передавал ОС с помощью таблицы $PIR и с помощью заполнения регистров 3Ch (INT_LN Interrupt Line (R/W)) и 3Dh (INT_PN Interrupt Pin (RO)) конфигурационного пространства PCI для каждой функции. Спецификация о таблице $PIR раньше была на сайте Microsoft, но сейчас её там уже нет. Содержимое строк таблицы $PIR можно понять из PCI BIOS Specification [4.2.2. Get PCI Interrupt Routing Options] или почитать вот тут

APIC

Предыдущий метод работал пока не появились многопроцессорные системы. Дело в том, что по своему устройству PIC может передавать прерывания только на один главный процессор. А хотелось бы, чтобы нагрузка на процессоры от обработки прерываний была сбалансированной. Решением данной задачи стал новый интерфейс APIC (Advanced PIC).

Для каждого процессора добавляется специальный контроллер LAPIC (Local APIC) и для маршрутизации прерываний от устройств добавляется контроллер I/O APIC. Все эти контроллеры объединяются в общую шину с названием APIC (новые системы сейчас уже соединяются по стандартной системной шине).

Когда прерывание от устройства приходит на вывод I/O APIC, контроллер направляет прерывание в LAPIC одного из процессоров. Наличие I/O APIC позволяет сбалансировано распределять прерывания от внешних устройств между процессорами.

Первой микросхемой APIC был 82489DX, это был отдельный чип, соединяющий в себе LAPIC и I/O APIC. Для создания системы из 2 процессоров нужно было 3 таких микросхемы. 2 функционировали бы как LAPIC и одна как I/O APIC. Позднее функциональность LAPIC была напрямую включена в процессоры, а функциональность I/O APIC была оформлена в чип 82093AA.

I/O APIC 82093AA содержала 24 входных вывода, а архитектура APIC могла поддерживать до 16 CPU. Для поддержки совместимости со старыми системами, прерывания 0~15 отвели под старые прерывания ISA. А прерывания от PCI устройств стали выводить на линии IRQ 16-23. Теперь можно было не задумываться о конфликтах прерываний от ISA и PCI устройств. Также благодаря увеличенному количеству свободных линий прерываний возможно стало также увеличить количество линий PIRQx.

Программирование I/O APIC и LAPIC осуществляется через MMIO. Регистры LAPIC расположены обычно по адресу 0xFEE00000, регистры I/O APIC по адресу 0xFEС00000. Хотя в принципе все эти адреса возможно переконфигурировать.

Как и в случае с PIC первоначально отдельные микросхемы позже вошли в состав чипсета.

В дальнейшем архитектура APIC получила модернизацию и новый вариант получил название xAPIC (x — extended). Сохранена обратная совместимость с предыдущим вариантом. Количество возможных CPU в системе увеличилось до 256.

Следующий виток развития архитектуры получил название x2APIC. Количество возможных CPU в системе увеличилось до 2^32. Контроллеры могут работать в режиме совместимости с xAPIC, а могут в новом режиме x2APIC, где программирование LAPIC осуществляется не через MMIO, а через MSR регистры (что гораздо быстрее). Cудя по этой ссылке для работы этого режима необходима поддержка IOMMU.

Следует заметить, что в системе может быть несколько контроллеров I/O APIC. Например один на 24 прерывания в южном мосту, другой на 32 в северном. В контексте I/O APIC прерывания часто обозначаются GSI (Global System Interrupt). Так вот в такой системе будут GSI 0-55.

Есть ли в CPU встроенный LAPIC и какой именно архитектуры можно понять по бит-флагам в CPUID.

Чтобы система могла обнаружить LAPIC и I/O APIC, BIOS должен представить информацию о них системе либо через таблицу MPtable (старый метод), либо через таблицу ACPI (таблицу MADT в данном случае). Помимо общей информации, и в MPtable и в ACPI (на этот раз в таблице DSDT) должна содержаться информация о роутинге прерываний, то есть информация о том, какое устройство сидит на какой линии прерываний (аналог таблицы $PIR).

О таблице MPTable можно почитать в официальной спецификации. Раньше спецификация была на сайте Intel, а сейчас её можно найти только в архиве. Спецификация ACPI сейчас расположена на сайте UEFI (текущая версия 6.2). Следует отметить, что с помощью ACPI можно указать роутинг прерываний и для систем без APIC (вместо использования таблицы $PIR).

MSI

Предыдущий вариант с APIC хорош, но не лишён недостатков. Все эти линии прерываний от устройств усложняют схему, и увеличивают вероятности ошибок. На смену шины PCI пришёл PCI express, в котором линии прерываний решили просто-напросто убрать. Чтобы сохранить совместимость, сигналы о возникновении прерываний (INTx#) эмулируются отдельными видами сообщений. В этой схеме логическое сложение линий прерываний, которое раньше производилось физическим соединением проводов, легло на плечи PCI мостов. Однако поддержка legacy INTx прерываний — это лишь поддержка обратной совместимости с шиной PCI. На деле PCI express предложил новый метод доставки сообщений о прерываниях — MSI (Message Signaled Interrupts). В этом методе для сигнализации о прерывании устройство просто производит запись в MMIO область отведённую под LAPIC процессора.

Если раньше на одно PCI устройство (то есть на все его функции) выделялось всего 4 прерывания, то сейчас сейчас стало возможным адресовать до 32 прерываний.

В случае с MSI нет никакого sharing для линий, каждое прерывание соответствует своему устройству.

Прерывания MSI решают также ещё одну проблему. Допустим устройство проводит memory-write транзакцию, и хочет сообщить о её завершении через прерывание. Но write транзакция может быть задержана на шине в процессе передачи (о чём устройство никак не знает), и сигнал о прерывании придёт до процессора раньше. Таким образом CPU будет читать ещё невалидные данные. В случае если используется MSI, информация об MSI передаётся также как и данные, и раньше прийти просто не сможет.

Следует заметить, что прерывания MSI не могут работать без LAPIC, но использование MSI может заменить нам I/O APIC (упрощение дизайна).

В последствии данный метод получил расширение MSI-X. Теперь каждое устройство может иметь до 2048 прерываний. И стало возможным указывать индивидуально каждому прерыванию на каком процессоре оно должно выполняться. Это может быть очень полезно для высоконагруженных устройств, например сетевых карт.

Для поддержки MSI не требуется никаких дополнительных таблиц BIOS. Но устройство должно сообщить о поддержке MSI в одной из Capability в своём PCI Config, а драйвер устройства должен поддерживать работу с MSI.

Заключение

В данной статье мы рассмотрели эволюцию контроллеров прерываний, и получили общую теоретическую информацию о доставке прерываний от внешних устройств в x86 системе.

В следующей части мы посмотрим как на практике задействовать в Linux каждый из описанных контроллеров.

Ссылки:

- Interrupt Controllers (Stuff in the Middle)

- What do the different interrupts in PCIe do?

- Reducing Interrupt Latency Through the Use of Message Signaled Interrupts

- Архитектура обработки прерываний в Intel совместимых системах

APIC Mode

Опция отвечает за включение расширенного контроллера прерываний (APIC — Advanced Programmable Interrupt Controller). Расширенный контроллер прерываний впервые начал применятся на двухпроцессорных материнских платах, т.к. там значительно сложнее обрабатывать прерывания от различных устройств (не совсем очевидно, какой из процессоров должен реагировать на прерывание). Затем расширенный контроллер прерываний «перекочевал» и на обычные однопроцессорные платы — устройствам становится доступно большее число прерываний (24 вместо 16), плюс, несколько плат расширения могут «висеть» на одном прерывании (иначе говоря, разделять его между собой). Если ваша операционная система поддерживает расширенный контроллер прерываний (Windows NT, Windows 2000, Windows XP, Windows 2003 и Windows Vista), включите (Enabled) данную опцию. В противном случае (в частности для Windows 95, Windows 98 и Windows Me) должно быть установлено значение Disabled.

Следует учитывать и еще один момент — расширенный контроллер прерываний является подсистемой расширенного конфигурирования и управления питанием (ACPI). Если вы отключите ACPI, вам придется отказаться и от использования расширенного контроллера прерываний.

Выбрать режим работы контроллера прерываний (расширенный или обычный) необходимо до установки операционной системы. Смена значения этой опции позднее способна нарушить ее нормальное функционирование. Обязательно задействуйте расширенный режим, если у вас многопроцессорная конфигурация, установлен процессор с виртуальной многопоточностью (Hyper-Treading) или имеющий несколько ядер. Иначе функционировать будет только один процессор (одно ядро), а остальные будут заблокированы.

APIC для многопроцессорных систем

В статье о прерываниях IRQ мы уже упоминали такой термин, как APIC. Возможно, читателям хотелось бы узнать чуть подробнее об этой технологии.

Сначала разберемся с тем, что же означает само это словосочетание. Аббревиатура APIC расшифровывается как Advanced Programmable Interrupt Controller (усовершенствованный программируемый контроллер прерываний).

Advanced Programmable Interrupt Controller – это контроллер прерываний, разработанный Intel и пришедший на смену ранее использовавшемуся контроллеру PIC (программируемому контроллеру прерываний).

Принцип работы контроллера

Контроллер выполнен в виде двух раздельных устройств. Одна часть контроллера размещена прямо в ядре процессора (так называемый Local APIC, или LAPIC), другая (I/O APIC) — на материнской плате.

Схема работы интерфейса Ввода / Вывода APIC через системную шину с встроенными в процессор

В современных компьютерах LAPIC содержится в каждом процессорном ядре, присутствующем в системе. В первых реализациях APIC LAPIC и I/O APIC были связаны друг с другом при помощи специальной шины. В современных системах для связи обеих контроллеров служит системная шина.

Преимущества

Основное преимущество APIC по сравнению с PIC – это поддержка многопроцессорных систем. Да и разрабатывался этот контроллер преимущественно для систем с несколькими процессорами. Все дело в том, что в системах, где установлено несколько процессорных ядер, крайне важно поддерживать параллельность работы всех процессоров. А для этого нужна была такая система, которая могла бы доставлять прерывания одновременно всем процессорам. Поэтому основная обязанность APIC – это распределение прерываний между процессорами.

В однопроцессорных системах введение APIC также оказалось полезным новшеством. В частности, Advanced Programmable Interrupt Controller позволил устройствам PCI отказаться от привязки к прерываниям шины ISA, что привело к улучшению производительности систем. Сам же набор стандартных прерываний был расширен с доступных в шине ввода/вывода ISA 16 прерываний до 24.

История возникновения

APIC впервые появился в системах, основанных на процессорах 486 DX. Сначала его предполагалось использовать лишь в многопроцессорных решениях, но впоследствии он появился и в однопроцессорных.

Процессор 486 DX поколения

В системах, основанных на процессорах 486, а также ранних Pentium (до архитектуры P54C), контроллер LAPIC был установлен не в процессоре, а на системной плате.

Полностью поддержка контроллера на уровне ОС появилась лишь начиная с Windows XP, в Windows 2000 была доступна лишь ограниченная поддержка.

Присутствие в BIOS

Большинство пользователей компьютера может при желании включить или выключить поддержку данной технологии в программе BIOS Setup. Обычно для этой цели служит опция BIOS ACPI APIC Support. Однако стоит помнить, что отключение поддержки APIC в BIOS обычно приводит к невозможности загрузки современных операционных систем, начиная с Windows 2000. При этом многие старые ОС, такие как Windows 95, 98 и ME могут нестабильно работать с этой опцией, поскольку они разрабатывались с учетом поддержки PIC.

Также стоит учитывать, что поддержка APIC является составной частью технологии ACPI, поэтому если вы выключите в BIOS саму поддержку ACPI, то вы не сможете использовать и Advanced Programmable Interrupt Controller.

Заключение

APIC – новый, разработанный компанией Intel программируемый контроллер прерываний, впервые использовавшийся в системах, основанных на старших моделях линейки процессоров Pentium. Введение этого контроллера позволило улучшить обработку прерываний, как в многопроцессорных, так и в однопроцессорных решениях.

Оптимизация производительности для платформ AMD

Настройка BIOS для платформ AMD EPYC и Ryzen Threadripper

Перечислены основные настройки, требующие внимания. Названия настроек могут отличаться от указанных. Сверьтесь с документацией по настройке BIOS для вашей платформы.

- Режим одной NUMA-ноды на CPU. Разбивать один CPU на несколько нод не рекомендуется: NUMA Nodes Per Socket: NPS1

- Включение Extended APIC. Рекомендуется для серверных CPU: Local APIC mode: x2APIC

- Поддержка виртуализации: SVM: Enabled

IOMMU: Enabled - Режим максимальной производительности CPU: Determinism Control: Enable

Determinism Slider: Power - Отключение энергосбережения на шине для предотвращения потерь пакетов: APBDIS: 1

Fixed SOC P-State: P0 - Приоритетный режим работы I/O PCI-устройства. Включается для одной сетевой карты указанием номера её PCI-шины. При наличии нескольких карт включается для той, где наблюдается пониженная производительность: Preferred IO: Manual

Preferred IO Bus:

Enhanced Preferred IO Mode: Enabled - Поддержка 10-битного расширенного тэга для устройств PCIe Gen 4: PCIe Ten Bit Tag Support: Enable

- Режим Relaxed Ordering для увеличения пропускной способности шины: Relaxed Ordering: Enabled

- Установка

- VM Appliance

- Ansible

- Режим кластера

- VPN (wireguard)

- Общее хранилище

- Отказоустойчивое хранилище

- Внешнее хранилище

- Гибридные схемы

- Подготовка системы

- Установка MITIGATOR

- Задачи администратора

- Резервное копирование

- Обновление

- Обновление до v23.12

- Обновление до v23.06

- Обновление до v23.02

- Обновление до v22.12

- Обновление до v22.08

- Обновление до v22.06

- Обновление до v22.02

- v23.12

- v23.08

- v23.06

- v23.02

- v22.12

- v22.08

- v22.06

- v22.04

- v22.02

- v21.12

- v21.10

- v21.06

- v21.04

- fail2ban

- log2ban

- MITIGATOR Challenge Response

- Logan

- Внешние скрипты

- Синхронизация ISN

- FastNetMon

- Весточка

- Prometheus

- Функциональные возможности

- Интеграция в сеть

- Быстрая настройка

- Сигнализация по BGP

- Чек-лист настройки системы

- Чек-лист настройки политики

- Аппаратный байпас

- Изоляция ядер

- Графики

- Grafana

- Отдельный Graphite

- Конфигурация ClickHouse

- Внешняя Grafana

- Единый Graphite

- Время хранения метрик

- Пример: MCR UDP

- Справочник

- Работа с сервисом

- Payload Analyzer

- Multipurpose Analyzer

- TLS Analyzer

- IP Analyzer

- ACL Rules Generator

- Support bot