Icarus Verilog

Icarus Verilog представляет собой одну из реализаций языка описания аппаратуры Verilog. Программное обеспечение Icarus Verilog позволяет моделировать и синтезировать электронные схемы, используя язык описания электронных схем Verilog. Icarus Verilog работает как компилятор, компилируя исходный код, записанный на языке Verilog в заданный формат. Для пакетного моделирования компилятор создает промежуточный формат, называемый vvp сборкой (vvp assembly). Этот промежуточный формат запускается на выполнение командой vvp. Icarus Verilog может быть бесплатно загружен с официального сайта http://bleyer.org/icarus или здесь. Icarus Verilog работает в режиме командной строки.

При моделировании с помощью языка Verilog каждая схема представляется набором модулей (module). Модулем называется самостоятельный компонент аппаратного обеспечения, имеющий входы и выходы. Можно выделить два основных способа описания работы модуля: поведенческий (behavioral) и структурный (structural). Поведенческие модели описывают что делает модуль, а структурные модели описывают из каких более простых модулей состоит описываемый модуль.

На языке Verilog модуль описывается специальной синтаксической конструкцией, которая начинается ключевым словом module и заканчивается ключевым словом endmodule. После ключевого слова module записывается название модуля, задаваемое разработчиком, после которого в круглых скобках приводится список входных и выходных переменных модуля.

Рассмотрим, для примера, как с помощью Verilog моделируется схема полусумматора.

Законченная программа моделирования полусумматора может быть записана в одном файле с помощью текстового редактора типа «Блокнот». Имя файла может быть любым, например, half_adder_test.v, где после имени файла через точку указывается рекомендуемое расширение v. Содержимое файла может быть примерно таким.

module half_adder(input a, b, output c, s); assign c = a & b; assign s = a ^ b; endmodule module test(); reg a, b; wire c, s; half_adder dut(a, b, c, s); initial begin $display("a b c s"); $monitor("%b %b %b %b", a, b, c, s); a = 0; b = 0; #10; b = 1; #10; a = 1; b = 0; #10; b = 1; #10; end endmodule

Как видно, содержимое файла состоит из двух модулей. Содержимое каждого модуля включается между зарезервированными словами module и endmodule. После слова module в первой строке описания модуля указывается имя модуля, после которого в скобках записываются параметры модуля, примерно так же как задаются функции в Си-подобных языках.

В данном примере первый модуль half_adder описывает непосредственно полусумматор, имеющий два входа (input) a и b, и два выхода (output) c и s. Тело модуля содержит два оператора assign, с помощью которых вычисляются значения выходов по заданным значениям входов с использованием логических операций & (логическое И) и ^(исключающее ИЛИ). Поскольку язык Verilog предназначен в первую очередь для описания цифровых схем, то его переменные по умолчанию принимают логические значения 0 и 1.

Оператор assign представляет собой оператор непрерывного присваивания (continuous assignment statement). Всякий раз когда входные переменные в правой части оператора непрерывного присваивания изменяются, переменные в левой части оператора присваивания вычисляются заново.

Второй модуль test является вспомогательным и предназначен для тестирования работы полусумматора. Оператор initial выполняет все операторы в своем теле в начале моделирования. Директивы begin и end представляют собой операторные скобки. Для задания временных задержек используется запись вида #10, означающая временную задержку на 10 единиц времени. Сигналы, используемые в блоке initial должны быть заданы с типом reg.

Функция $display(«a b c s») выводит строку, указанную в качестве ее параметра на консоль.

Функция $monitor(«%b %b %b %b», a, b, c, s) задает вывод сигналов a, b, c, s на консоль, а строка «%b %b %b %b» определяет формат вывода, в данном случае выводятся двоичные значения сигналов.

Чтобы с помощью этого файла промоделировать заданную схему, можно использовать программу Icarus Verilog. В каталоге my_samples имеются готовые пакетные файлы ivrl.bat и ivrl_view.bat, облегчающие работу с программой. Разместите в этом каталоге исходный файл, запустите из данного каталога окно командной строки и наберите команду ivrl.bat, после которой укажите в качестве параметра имя созданного файла (без расширения). Если все сделано правильно, должны появиться данные, отражающие результаты моделирования, как показано на рисунке.

Для более наглядного представления о поведении сигналов во времени можно воспользоваться графическим интерфейсом GTKWave. Для этого нужно в окне командной строки задать команду ivrl_view.bat, указав в качестве параметра имя созданного файла (без расширения). В результате появится окно программы с загруженными результатами моделирования.

Чтобы увидеть сигналы, в левом верхнем окошке щелчком на + разверните пункт test, и щелкните на пункте dut. В результате этого в среднем окошке должны появиться названия сигналов. Выделение сигналов и нажатие кнопки Append приводит к их появлению в основном окне. Результат должен выглядеть примерно так, как показано на рисунке.

Команда iverilog: опции, ключи и примеры использования

Общие команды – Общие команды, присущие различным операционным системам.

iverilog

Preprocesses and compiles Verilog HDL (IEEE-1364) code, into executable programs for simulation. More information: http://iverilog.icarus.com/.

- Compile a source file into an executable:

- Also display all warnings:

- Compile and run explicitly using the VVP runtime:

- Compile using Verilog library files from a different path:

- Preprocess Verilog code without compiling:

Примеры кода, демонстрирующие общие подходы в программировании или же решающие небольшие прикладные задачи. Языки программирования и библиотеки, позволяющие эффективно решать задачи разработки. Объектно-ориентированное программирование, функциональное программирование и прочие подходы и …

Трюки Bash

Полезные заметки по работе с командной строкой: bash и прочие *sh. Однострочники, скрипты, позволяющие решать большие и малые задачи администрирования и настройки Юникс систем. Zsh для современного MacOS, Bash для …

Заметки о настройке различных IT-штуковин. Настройка, допиливание, полировка. Конфигурируем приложения и тюнингуем сервера. Полезные параметры и ключи запуска программ. Увеличиваем скорость, уменьшаем отклик, ускоряем работу и улучшаем результаты работы. Объясняем …

Терминал/Консоль

Команды и инструкции терминала (консоли) Linux, MacOS, Windows и прочих операционных систем. Трюки и особенности командных оболочек, скрипты для администрирования Unix. Программирование и скриптование Windows и Linux, тонкая настройка Macos. …

Также может быть вам интересно:

- Как получить дерево директорий на Bash одним однострочником

- Python: Функции

- Python: Встроенные типы данных (list, set, dict, etc)

- Python: типы данных, переменные, логическое ветвление и циклы

- Как сделать свою middleware в Django (с примерами)

Свежее на «Цифре»

MessageId или как дебажить систему с минимумом проблем

Программы, 09.09.2023

Проверочный список для выпуска промышленных приложений с иллюстрациями

Работа и управление, 30.07.2023

В Google Pixel и Windows Snipping Tool есть возможность восстановления обрезанных изображений

Новости, 23.03.2023

Два подарка «под ёлочку» от Heroes of Might and Magic

Новости, 25.12.2022

Вышел Pulsar – редактор кода на основе Atom

Новости, 25.12.2022

Ленивый backup PostgreSQL

Программы, 17.12.2022

Google анонсировала OSV-Scanner: сканер уязвимостей в программных проектах

Новости, 16.12.2022

Gitea запускает коммерческую версию, а недовольные – форк Forĝejo

На днях группа бывших разработчиков Gitea решили создать на базе хостинга кода Gitea свою версию проекта – «Forgejo». Причиной тому …

Пользователи и их создание в Django — своя регистрация на сайте

Если вашим сайтом должны активно пользоваться несколько человек, то полезно их различать, а значит — надо уметь создавать пользователей, либо …

Новый синтаксис старой команды with в Python 3.10

Как же долго моё чувство прекрасного страдало… Но в Python 3.10 появился новый парсер синтаксических конструкций Python!

Добавляем постраничную пагинацию на Django сайт

На сайтах часто встречаются многостраничные объекты: список товаров, список заметок и т.д. Поэтому важно уметь добавить навигацию по страницам на …

Новый оператор match-case в Python

В новой версии Python (3.10) появится новый оператор. Новый оператор сопоставления по шаблону (match-case).

Нет слов, одни. однострочники

На днях вышел пост со списком полезных однострочников для JavaScript программистов. Памятуя Perl-овую молодость, заглянул туда.

Добавляем переменные в контекст Django шаблонов (свой контекст-процессор)

В Django вы можете передавать данные в шаблоны посредством контекстов. Контекст передаётся из контроллера (view в терминах Django), однако, если …

Пример своей консольной команды в Django проекте

Если вы работали с Django проектом, то, скорее всего, запускали команды из консоли (manage.py). В Django есть простой способ писать …

Разграничение прав доступа на Django сайте

Почти на любом веб-сайте необходимо разделять пользователей на группы и предоставлять им разные возможности. В Django есть довольно серьёзная система …

Icarus verilog как использовать

Всем привет! Пока еще не запретили Интернет и всякие китайские товары (вещание происходит из чревовещателя за 14 апреля 2022 ужасного года), я бродкастирую (вещаю) из своего уютного бункера. Сегодня я решил начать серию рассказов о том, каким образом можно создать простую схемку, а потом чуть более сложную схему и запустить ее выполняться на верилоге.

Первое и самое важное, что я хочу сказать — работать я буду только в linux ubuntu, потому что там есть необходимое мне для работы программное обеспечение. Для винды не знаю, не пробовал, потому без понятия, как там настроить нормально. Например, если еще в винде есть iverilog и прочие ништяки, то verilator что-то на горизонте не наблюдался, либо я искал плохо.

Итак, что требуется для установки (sudo apt install):

- iverilog gtkwave — для синтеза

- verilator — для тестирования

- libsdl2-2.0-0 libsdl2-dev — для запуска теста

После того, как все установлено, можно начинать кодить.

§ Самый простой проект

Пользоваться будем компилятором icarus verilog и потому я создам самый простой проект в истории человечества, а именно hello world. Файл назову tb.v:

1`timescale 10ns / 1ns 2module tb; 3 4 reg clock; 5 always #0.5 clock = ~clock; 6 initial begin clock = 0; #2000 $finish; end 7 8endmodule

Разберу построчно.

- `timescale 10ns / 1ns — это директива компилятору и симулятору, что минимальной единицей измерения является 1 наносекунда, а единицей отсчета — 10 наносекунд. Это примерно как 1 миллиметр и 10 миллиметров (1 сантиметр). Отсчеты ведутся именно на 10ns.

- module tb; . endmodule — начало и завершение модуля (обертка модуля)

- reg clock; — объявление регистра clock. Регистр — это 1 бит памяти, который может хранить либо 0, либо 1

- initial begin clock = 0; #2000 $finish; end — инициализация при старте кода, вначале регистру clock присваивается значение 0, и спустя 2000*10ns (указано в timescale) = 20 000 нс, или 20 микросекунд, симуляция будет завершена

- always #0.5 clock = ~clock; — эта конструкция означает, что каждые 0.5*10 нс или каждые 5 нс будет перебрасываться из 0 в 1, и из 1 в 0, тем самым симулируется тактовый генератор.

§ Создание makefile

Обычно я люблю создавать makefile для того, чтобы выполнять разные рутинные действия:

1all: 2 iverilog -g2005-sv -DICARUS=1 -o tb.qqq tb.v 3 vvp tb.qqq >> /dev/null

Компиляция

- iverilog -g2005-sv -DICARUS=1 -o tb.qqq tb.v — это компилятор, который компилирует файл tb.v в tb.qqq

- -g2005-sv — опция означает, что используется system verilog 2005

- -DICARUS=1 — передача параметр ICARUS=1, то есть, делается #define ICARUS 1, параметров может быть много

- -o tb.qqq — куда выгрузить откомпилированный файл

vvp tb.qqq >> /dev/null

Эта программа приблизительно симулирует поведение верилог-файла, который был передан. Результаты выгружаются отдельно, команда, которая выгружает результаты, задается в tb.v файле:

1module tb; 2. 3initial begin $dumpfile("tb.vcd"); $dumpvars(0, tb); end 4. 5endmodule;

Что означает:

- $dumpfile(«tb.vcd»); — команда говорит, что результаты симуляции будут выгружены в tb.vcd файл

- $dumpvars(0, tb); — то, из какого модуля будут выгружены результаты

Помимо значений регистров и проводов в модуле, будут выгружены также результаты из всех субмодулей, если они есть.

§ Отладка

После компиляции появится 2 новых файла:

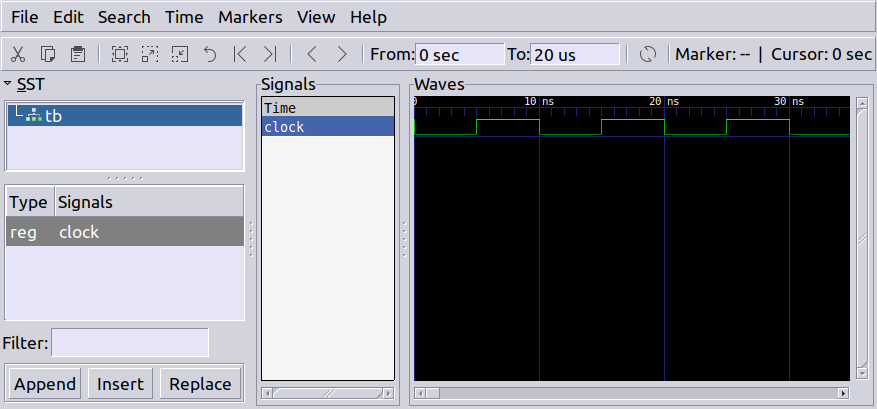

Чтобы посмотреть, что получилось в симуляции, я пользуюсь GtkWave, для этого надо запустить команду gtkwave tb.vcd .

Перед тем, как сигнал посмотреть, надо выбрать модуль, потом выбрать один из проводов или регистров и добавить через Append. Обновлять сигналы можно через сочетание клавиш ctrl+shift+r, чтобы не перезагружать снова.

После того, как сигналы были добавлены, можно сохранить их через ctrl+s, выбрав имя, например, tb.gtkw. Теперь же, после каждой загрузки можно не добавлять сигналы снова, а просто вызвать команду gtkwave tb.gtkw .

§ Verilator

Признаюсь, верилятор я освоил совсем недавно и был крайне удивлен тому, как он работает и вообще, считаю его самым интересным инструментом для работы. К нему я еще могу вернуться в будущем, когда буду делать видеоадаптер. А сейчас пока что расскажу как первично его настроить.

Для чего нужен верилятор вообще? Собственно, только для того, чтобы преобразовать модуль из верилога в c++ код, представить его полный эквивалент, чтобы потом использовать в тестировании кода вне ПЛИС-а.

Как обычно, сначала перейдем к рассмотрению makefile

1VINC=/usr/share/verilator/include 2 3all: 4 verilator -Wall -Wno-unused -cc tb.v 5 cd obj_dir && make -f Vtb.mk 6 g++ -o tb -I$(VINC) tb.cc $(VINC)/verilated.cpp obj_dir/Vtb__ALL.a

Теперь внимательно разберусь с каждым пунктом:

- VINC=/usr/share/verilator/include — это путь к библиотекам верилятора, очень важно

- verilator -Wall -Wno-unused -cc tb.v — собственно, компиляция tb.v

- cd obj_dir && make -f Vtb.mk — переход в рабочий каталог и сборка

- g++ -o tb -I$(VINC) tb.cc $(VINC)/verilated.cpp obj_dir/Vtb__ALL.a — строка компиляции С++ файла

Есть момент такой, что когда синтезируется модуль tb, то имя его класса в С++ становится Vtb — то есть, приписывается V вначале (от слова Verilated, я так понимаю). Здесь obj_dir/Vtb__ALL.a — это архивированные коды для дальнейшего их использования в линковщике g++.

Итак, теперь рассмотрим то, что находится в tb.cc:

1#include "obj_dir/Vtb.h" 2 3int main(int argc, char **argv) < 4 5 Verilated::commandArgs(argc, argv); 6 Vtb* top = new Vtb; 7 8 top->a = 0; 9 10 // Обработка 10 тактов 11 for (int i = 0; i < 10; i++) < 12 13 top->eval(); 14 printf("i=%d | a=%d, b=%d\n", i, top->a, top->b); 15 top->a = !top->a; 16 17 if (Verilated::gotFinish()) break; 18 > 19 20 delete top; 21 return 0; 22>

Этот код можно считать неким таким шаблонов для тестбенчей на вериляторе.В самом начале подключается необходимый h-файл:

#include "obj_dir/Vtb.h"

А потом создается объект класса:

Vtb* top = new Vtb;

При каждом запуске обязательно надо инициализировать код:

Verilated::commandArgs(argc, argv);

Инициализируется top->a = 0; стартовое состояние входа a . Выполняется 10 тактов. На каждом такте происходит исполнение модуля, симуляция:

top->eval();

И потом значение входа меняется на противоположное:

top->a = !top->a;

И так 10 раз.

В результате выполнения программы получается следующее:

i=0 | a=0, b=1 i=1 | a=1, b=0 i=2 | a=0, b=1 i=3 | a=1, b=0 i=4 | a=0, b=1 i=5 | a=1, b=0 i=6 | a=0, b=1 i=7 | a=1, b=0 i=8 | a=0, b=1 i=9 | a=1, b=0

Icarus verilog как использовать

Verilator — это бесплатный программный инструмент с открытым исходным кодом, который преобразует Verilog/SystemVerilog в поведенческую модель с точностью до такта на C++ или SystemC. Создаваемые модели являются точными с точки зрения цикла и имеют два состояния; как следствие, такие модели обычно обеспечивают более высокую производительность, чем более широко используемые событийно-ориентированные симуляторы, которые могут моделировать поведение в пределах тактового цикла. В настоящее время Verilator используется в академических исследованиях, проектах с открытым исходным кодом и для коммерческой разработки полупроводниковых микросхем. 1. Установка программного симулятора — Verilator Установка программы Verilator для ОС Arch Linux осуществляется следующей инструкцией pamac install verilator После установки убедитесь в корректности, запросив текущую версию программы verilator —version Удаление производится следующей инструкцией

Лабораторная работа № 2

Исследование процессорной архитектуры RISC_V на основе микропроцессорного модуля BL808 Цели работы: Исследование процессорной архитектуры RISC_V Исследование аппаратного таймера процессора Интеграция пользовательского модуля низкоресурсного криптографического алгоритма Данная лабораторная работы выполняется на основе процессорного модуля M1s DOCK установленного на плате. 1. Подготовка к работе

Лабораторная работа №1

Исследование программного симулятора QEMU на основе процессорной архитектуры RISC-V Цели работы: Исследование программного пакета QEMU для эмуляции аппаратного обеспечения процессоров Исследование процессорной архитектуры RISC_V a. Исследование аппаратного модуля UART b. Исследование аппаратного модуля прямого доступа к памяти (DMA) Изучение принципов работы компоновщика (Linker Script) Краткая теоретическая справка