Крепёжные отверстия в печатной плате

1. Оборудование для сверления печатных плат может использовать сверла диаметром до 6,0мм (и до 6,5мм иногда). По этой причине крепежные отверстия правильнее задавать pinом (padом и т.п. в зависимости от САПР).

2. Допускается. Главное чтобы центр линии обозначал контур, а не внешняя или внутренняя ее граница.

3. Стеклотекстолит может выкрошиться. Есть неписанное правило — отступ отверстия от края должен быть не менее толщины печатной платы. Если все же по какой то причине нужно так близко, можете заменить отверстие на паз, выходящий на край платы.

4.1. Нужно.

4.2. Нужно на 0,20мм.

Пользователь

Сообщений: 7 Регистрация: 13/01/14

14/01/14 9:32:33

Спасибо! Позвольте уточнить:

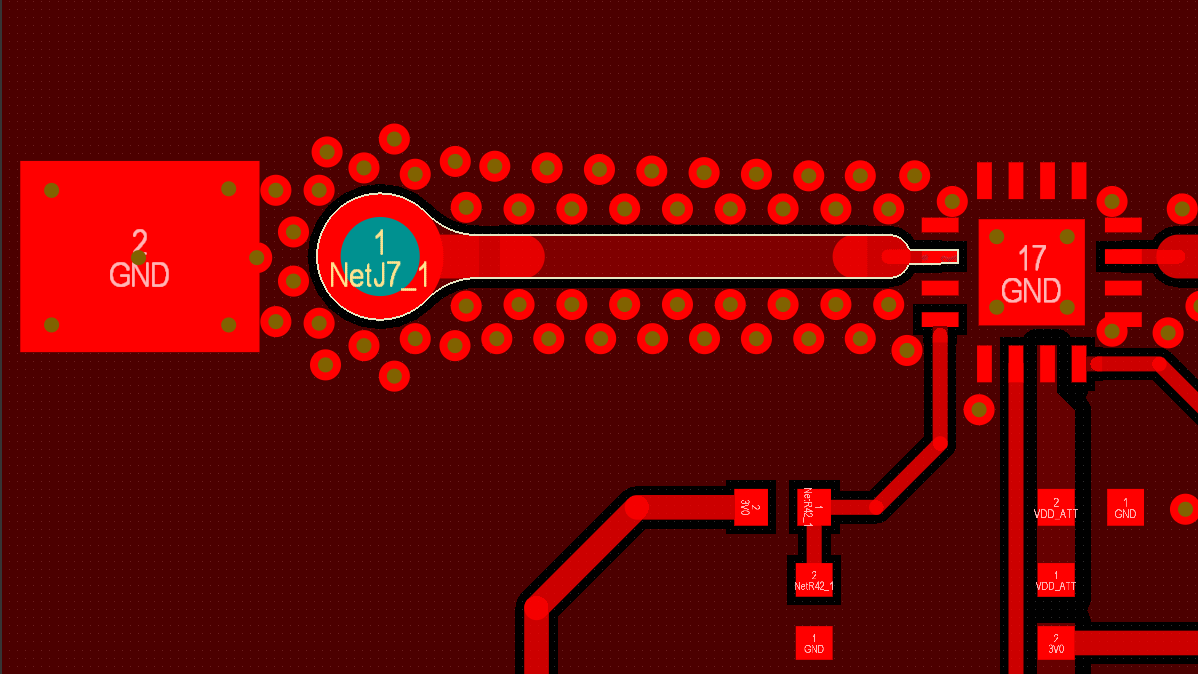

1. Т.е. Вы имеете ввиду вот так?

обычное отверстие (Pad), в настройках отключается Plated (металлизация) и гарантированный поясок меди убирается полностью.

2. Еще один вопрос возник, как грамотно показать продолговатые контактные площадки и их отверстия под медные шины? и возможна ли их металлизация?

На фото: внешние: 10MMx5MM, отверстие: 7MMx3MM

Изменено: Игорь Никитин — 14/12/21 15:28:23

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

14/01/14 9:43:26

1. Именно так.

2. Насколько я понимаю, Вы правильно задали овальное металлизированное отверстие. Обычно в таких случаях присылают 2 файла в формате Excellon — круглые и пазы. В заказе для страховки обратите внимание на наличие металлизированных пазов.

Пользователь

Сообщений: 7 Регистрация: 13/01/14

14/01/14 10:15:32

Благодарю.Сейчас глянул — да, действительно, программа создала два файла:

***-RoundHoles.TXT

***-SlotHoles.TXT

Пользователь

Сообщений: 7 Регистрация: 13/01/14

18/01/14 0:09:43

Скажите, а какие есть ограничения по слотам? (соотношение сторон, . )

Пользователь

Сообщений: 245 Регистрация: 30/08/12

20/01/14 8:44:56

Минимальный диаметр фрезы — 1,0 мм. Минимальный радиус скругления таким образом 0,5 мм. Соответственно, ширина готового паза после металлизации ~0.9 мм. По соотношению сторон каких-то ограничений нет, но само собой нужно руководствоваться здравым смыслом.

Пользователь

Сообщений: 7 Регистрация: 13/01/14

20/01/14 11:54:17

Просто я видимо введен в заблуждение: где-то прочитал, что слоты делают не фрезой, а как то иначе и именно благодаря этому получаются ровные шершавые стенки для возможности выполнения металлизации.

Т.е. можно просто разместить много слотов с наложением?:

Но даже при смещении отверстий на минимальный шаг сетки получается не ровно:

либо это просто так отображается в Altium Designer 13

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

20/01/14 15:14:44

В Altium применяется т.н. метод DrillSlot — это когда паз получается сверлением, а не фрезерованием. Мы же просто фрезеруем во внутреннему контуру и и таких неровностей не образовывается.

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

20/01/14 15:15:27

Присылайте как есть, мы доработаем.

Пользователь

Сообщений: 5 Регистрация: 07/08/14

07/08/14 14:56:12

Добрый день. Подскажите есть крепежное отверстие (PAD) металлизация не нужна, но нужно сохранить отступ, поэтому отключаю опцию Plated, но при этом никаких визуальных изменений не происходит. И при передаче в гербер также никаких изменений не заметил. Вопрос как показать отсутствие металлизации?

Так же я использую чужие библиотеки импортированные из P-CADa, и у PADов под smd компоненты опция Plated так же снята по умолчанию, является ли это ошибкой? Работаю в Altium Designer

Прикрепленные файлы

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

07/08/14 15:50:18

Главным условием наличия металлизации в стакане отверстия является наличие металла (площадка или полигон) на верхней и нижней стороне платы.

С неметаллизированными несколько сложнее. Существует 2 метода получения таковых.

1. Посредством рассверливания на конечном этапе изготовления.

2. Получение неметаллизированных отверстий сверлением в один проход за счет тентирующих свойств фоторезиста.

Мы работаем по 2 методу. Для гаратированного отсутствия металлизации в стакане необходимо убрать весь металл над и вблизи отверстия (не ближе 250мкм).

Отсюда вывод — стоит или не стоит галка неважно. Для бОльшей гарантии можете экспортировать металлизированные и неметаллизированные отверстия в разные файлы. Altium это позволяет, а мы дополнительно все проверим.

Пользователь

Сообщений: 5 Регистрация: 07/08/14

07/08/14 17:53:31

То есть если, я отошлю вам гербер с таким отверстием как показал выше металлизации в нем не будет? и указывать ничего в сопроводительном письме не нужно?

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

08/08/14 16:06:19

Если честно, то по картинке я ничего не понял.

А для бОльшей гарантии можете экспортировать металлизированные и неметаллизированные отверстия в разные файлы. Altium это позволяет, а мы дополнительно все проверим.

Пользователь

Сообщений: 5 Регистрация: 07/08/14

08/08/14 16:16:05

Пользователь

Сообщений: 5 Регистрация: 11/04/18

20/11/18 16:50:51

Добрый день. Возможно ли выполнить отверстие указанное на рисунке?

Прикрепленные файлы

Изменено: Luba_vr — 20/11/18 16:52:29

Администратор

Сообщений: 927 Баллов: 3 Регистрация: 30/08/12

22/11/18 10:51:28

Здравствуйте.

Минимальная фреза в наличии 1,0мм. Сделаем без проблем.

Пользователь

Сообщений: 1 Регистрация: 04/07/20

04/07/20 20:39:16

С неметаллизированными несколько сложнее. Существует 2 метода получения таковых.

1. Посредством рассверливания на конечном этапе изготовления.

2. Получение неметаллизированных отверстий сверлением в один проход за счет тентирующих свойств фоторезиста.

Мы работаем по 2 методу. Для гаратированного отсутствия металлизации в стакане необходимо убрать весь металл над и вблизи отверстия (не ближе 250мкм).

Всегда делал крепёжные отверстия без металлизации. Кучу плат (разных проектов десятки) изготавливал в разных конторах, в т.ч. у вас в Резоните, и никогда не было вопросов по поводу крепёжных отверстий. Китайцы вообще никогда вопросов ни о чём не задавали, делали и всё. Но тут вдруг на днях при заказе у вас возникло требование отодвинуть металл от отверстий на 0.25мм. Я удивился вашему ответу, что сами вы это сделать не можете. Отверстия без металлизации сделаны в отдельном файле. Ну ладно, думаю, сделаю. Просмотрел в Альтиуме и что-то ничего там подобного не увидел. Гербер верхнего слоя открыл, там отверстия, конечно, нет. Там просто блямба меди по всей поверхности. Как открыть медь на 0.5мм больше диаметром, чем дырка?

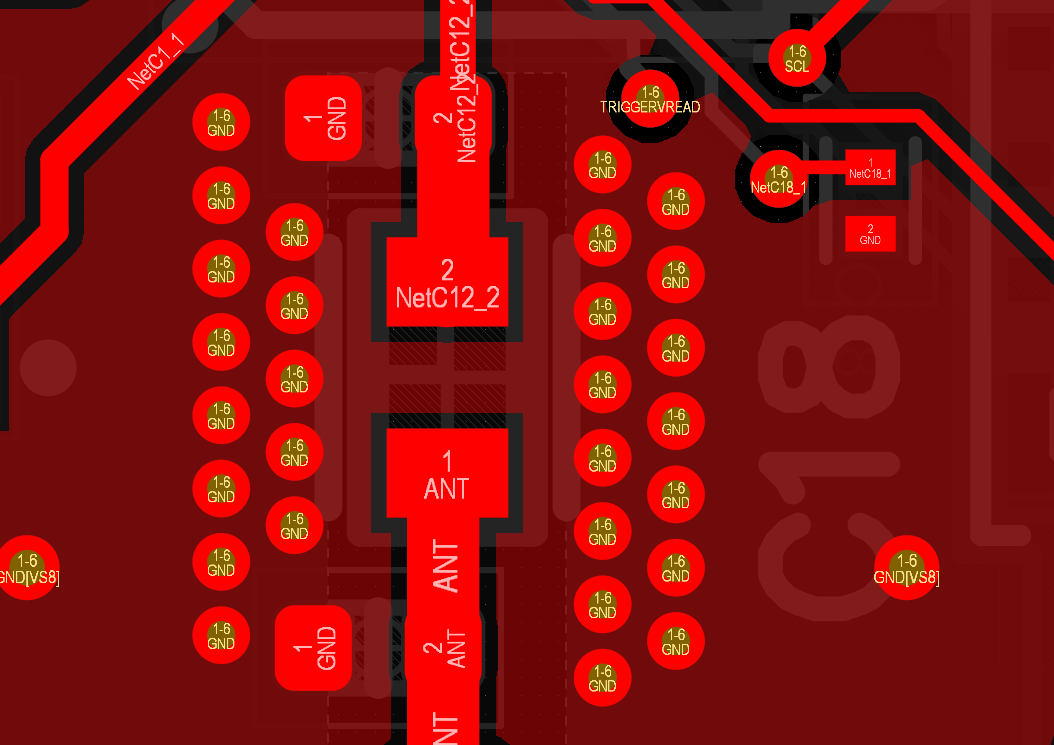

Все, что необходимо знать о сшивающих переходных отверстиях

Сшивающие переходные отверстия часто разбросаны по всему поверхностному слою печатной платы. Когда заливка медью используется грамотно, в идеале для сшивающих переходных отверстий рассчитывается такое разделительное расстояние, при котором массив переходных отверстий подавляет перекрестные наводки и помехи. Также их используют как несколько параллельных соединений между слоями, что может обеспечить низкое сопротивление и полное сопротивление, и, следовательно, высокий постоянный или переменный ток.

В этом руководстве я опишу стандартные варианты использования сшивающих переходных отверстий и ситуации, в которых их следует использовать на печатной плате. Этот раздел проектирования печатных плат вызывает разногласия среди проектировщиков, поскольку он связан с заливкой медью, которая, как часто утверждают, не требуется в большинстве конструкций. Как бы вы не относились к заливке медью, сшивающие переходные отверстия играют важную роль на печатных платах при низких и высоких частотах.

Основная информация о сшивающих переходных отверстиях на печатных платах

Сшивающие переходные отверстия имеют простую конструкцию. Это периодический массив переходных отверстий, как правило заземляемых через структуру слоев печатной платы. Таким образом, они формируют соединения между сетями заземления в нескольких слоях. В одном из вариантов использования массивов переходных отверстий присутствуют межслойные соединения питания (см. ниже). Эти структуры также играют важную роль в радиочастотных системах, и в ряде ситуаций сшивающие переходные отверстия используются неправильно.

Для быстрого знакомства с вариантами использования сшивающих переходных отверстий на печатной плате посмотрите следующее видео. К основным областям относятся проектирование высокоскоростных и радиочастотных печатных плат и маршрутизация питания через несколько слоев.

Подробнее рассмотрим каждую из этих областей:

Типовое использование: подключение заземления

Стандартный вариант использования сшивающих переходных отверстий — это соединение участков заземления через несколько слоев. На многослойной печатной плате обычно имеется несколько медных участков, относящихся к одной сети заземления. Сшивающие переходные отверстия — удобный инструмент для их соединения и обеспечения минимально возможного полного сопротивления для любых обратных токов, двигающихся вдоль опорной плоскости в печатной плате.

Это одна из областей, в которой сшивающие переходные отверстия, подсоединенные к заземлению, играют ценную роль. Переходы между слоями в цифровых и радиочастотных цепях должны иметь четкое опорное заземление для контроля над прохождением сигнала по межсоединению на печатной плате. При переходе между слоями близлежащее переходное отверстие в массиве сшивающих переходных отверстий может выполнять ту же функцию, что и плоскость заземления под трассой.

Как правило, когда массив сшивающих переходных отверстий помещается на печатную плату, одно из этих отверстий вероятно будет расположено рядом с переходом между слоями через сигнальное переходное отверстие. В каких-то ситуациях эта схема, вероятно, будет работать нормально, не придется беспокоиться об эмиссии помех или о подверженности помехам в зоне перехода через переходное отверстие. Присутствия заземленного сшивающего переходного отверстия рядом с сигнальным отверстием должно быть достаточно для подавления помех, особенно для медленных GPIO, I2C, UART и других медленных цифровых протоколов (так же, как и для низкочастотных аналоговых схем).

паразитную емкостную связь с другими сигнальными сетями. Такого же результата можно ожидать и здесь.

паразитную емкостную связь с другими сигнальными сетями. Такого же результата можно ожидать и здесь.

Сшивающие переходные отверстия и антиконтактные площадки влияют на полное сопротивление переходных отверстий

В результате изменения емкостного и реактивного сопротивления, описанного в предыдущем разделе, размещение сшивающих переходных отверстий в переходе между слоями будет определять полное сопротивление переходных отверстий. Связанный компонент — это антиконтактная площадка, которая в идеале должна пересекаться со сшивающими переходными отверстиями, вследствие чего они будут совместно изменять полное сопротивление. Большинство калькуляторов полного сопротивления переходных отверстий неспособны рассчитать фактическое полное сопротивление переходных отверстий из-за присутствия компоновок сшивающих переходных отверстий и размера антиконтактной площадки вокруг области перехода между слоями.

Хотя сшивающие переходные отверстия и антиконтактные площадки, проходящие через плоскости заземления, влияют на полное сопротивление, входное полное сопротивление на переходном отверстии не будет существенно отклоняться от 50 Ом (или дифференциала примерно в 100 Ом), пока частота не превысит примерно 3–5 ГГц. На низких частотах не нужно беспокоиться о том, насколько сильно сшивающие переходные отверстия и размер антиконтактных площадок влияют на полное сопротивление сшивающих переходных отверстий. Скорее всего, вы не заметите никакого эффекта, поскольку переходные отверстия будут очень электрически короткими. При частотах выше приблизительно 5 ГГц это играет очень важную роль, поскольку неверно размещенные сшивающие переходные отверстия и крупные антиконтактные площадки не будут обеспечивать достаточную емкостную нагрузку. Это приведет к индуктивному переходу переходных отверстий, при котором полное сопротивление достигает сотен Ом. Ниже показаны S-параметры для примера перехода переходного отверстия без сшивающих переходных отверстий и крупной антиконтактной площадки.

Короткий ответ: «да», но только до определенных частот. Используя их с целью экранирования, проектировщик, возможно, будет лишь догадываться о требуемом расстоянии между переходными отверстиями. В ряде ситуаций то, что мы называем экранированием в волноводах, правильнее было бы назвать локализацией поля. Невзирая на название, сшивающие переходные отверстия способны блокировать распространение электромагнитных волн вплоть до определенной максимальной частоты.

Для конкретной частоты, которую необходимо подавить, шаг между переходными отверстиями должен быть приблизительно таким:

прочитайте эту статью о заливке медью на макетах печатных плат, в которой описано влияние сшивающих переходных отверстий на шумовую связь и электромагнитные помехи.

Чтобы получить доступ к лучшим функциям САПР и средствам автоматизации для проектирования печатных плат, воспользуйтесь инструментами проектирования в Altium Designer®. Когда проектирование будет завершено, а данные готовы для передачи на производство, платформа Altium 365™ поможет наладить совместную работу и доступ к проектам. Информация о ежемесячных обновлениях функций в Altium Designer.

Мы лишь поверхностно рассмотрели некоторые возможности Altium Designer на Altium 365. Начните использование бесплатной пробной версии Altium Designer + Altium 365 сегодня .

Крепеж и зоны запрета в Altium

Один шагом проектирование печатной платы является обозначение зон, в которых запрещается размещение компонентов и проводников. Обычно эти зоны располагаются по краям платы и предназначены для крепления рамок, соединителей и т.п. Кроме того на плате могут быть вырезы, крепежные отверстия и другие области в которых нельзя проводить печатные проводники. Контур печатной платы, после создания, автоматически становится зной запрета для печатных проводников. Ширину запрещенной зоны от края платы устанавливается в правилах «Clearance». Для размещения зон запрета на плате используют команду Place>Keepout>SolidRegion. Во время создания полигона нажатием TABили двойным нажатием ЛКМ на готовый полигон открывается диалоговое окно Region в котором задаются свойства зоны запрета (см. Рис.1).  Рис.1. Свойства зоны запрета Если в поле Layerустановлен определенный слой, например BottomLayerкак на рисунке 1, то эта зона запрета будет действовать только для размещения компонентов и печатных проводников непосредственно в указанном слое. Для запрета в области выбранного полигона на все слои необходимо установить в графе Layer > Keep-Out layer. Так же зону запрета можно создать для определенной цепи, которая указывается в окне Net свойств полигона (см. Рис. 1). Крепежные отверстия устанавливаются командой Place>Pad, как обычные контактные площадки. После запуска команды размещения отверстий следует нажать клавишу Tab и в свойствах (см. Рис.2) указать нулевые значения в параметрах формы контактной площадки (Size and Shape) и при необходимости отключить металлизацию внутри отверстия (Plated).

Рис.1. Свойства зоны запрета Если в поле Layerустановлен определенный слой, например BottomLayerкак на рисунке 1, то эта зона запрета будет действовать только для размещения компонентов и печатных проводников непосредственно в указанном слое. Для запрета в области выбранного полигона на все слои необходимо установить в графе Layer > Keep-Out layer. Так же зону запрета можно создать для определенной цепи, которая указывается в окне Net свойств полигона (см. Рис. 1). Крепежные отверстия устанавливаются командой Place>Pad, как обычные контактные площадки. После запуска команды размещения отверстий следует нажать клавишу Tab и в свойствах (см. Рис.2) указать нулевые значения в параметрах формы контактной площадки (Size and Shape) и при необходимости отключить металлизацию внутри отверстия (Plated).  Рис.2. Свойства контактной площадки для крепежных отверстий Стоит отметить, что при формировании контура платы посредством импорта модели платы в формате STEP, будет автоматически созданы отверстия, в свойствах которых включена металлизация и сформирован поясок металлизации, равный диаметру отверстия.

Рис.2. Свойства контактной площадки для крепежных отверстий Стоит отметить, что при формировании контура платы посредством импорта модели платы в формате STEP, будет автоматически созданы отверстия, в свойствах которых включена металлизация и сформирован поясок металлизации, равный диаметру отверстия.

Altium — Пранович В. 11. Altium Designer (build 7.х). Проект многослойной печатной платы: выбор стека и задание общих правил проекта

Все действия приведены для версии Altium Designer Summer 08. В данной статье рассмотрены не только вопросы, касающиеся многослойных печатных плат, но и другие аспекты работы в пакете Altium Designer.

В статье будут обсуждены следующие темы:

• создание схем, в которых содержатся элементы, требующие выравнивания длин топологических связей или использования дифференциальных линий;

• создание правил трассирования в редакторе для электрических схем;

• написание конкретных правил для топологии и рассмотрение их действия;

• топология многослойной печатной платы со сквозными переходными отверстиями;

• типовые сопутствующие проблемы проектирования печатных плат.

Автор не станет придерживаться последовательности действий, использованных на практике при реализации этого проекта. Мы укажем только те из них, которые могут быть использованы при проектировании многослойных печатных плат, а также раскроем суть и очередность действий для достижения тех или иных целей. Автор не настаивает на исключительности данных действий, а приводит их как результат практического применения в конкретном примере.

При разработке многослойных печатных плат следует ответственно подходить ко всем настройкам параметров как самого проекта, так и всех элементов, которые будут применены в нем. Как правило, такие проекты содержат значительное число элементов разнообразных типов, включая многовыводные посадочные места. Отсюда высокие требования к размещению компонентов в заданной зоне печатной платы, которые должны учитывать и другие специфические особенности топологии.

В данном примере мы будем рассматривать, в основном, вопросы обращаясь к библиотекам только при необходимости.

Общие требования к проекту

Сформулируем основные требования к проекту, которые должны быть учтены в данном примере и перенесены в топологию печатной платы. Для учета данных требований и их проверки необходимо создать правила, которые, если это возможно, должны быть представлены на электрической схеме.

Итак, эти требования таковы:

1. Все компоненты должны располагаться только с одной стороны печатной платы.

2. Верхний и нижний слои должны быть отведены только под экранирующие полигоны.

3. Стек слоев должен содержать не менее двух типа Plane для электрической цепи «общая земля».

4. Стек должен содержать как минимум один слой типа Plane для шин питания.

5. Под шины питания и другие цепи с высоким значением тока должен быть отведен один специальный сигнальный слой.

6. Один сигнальный слой должен быть отведен только для скоростных дифференциальных сигналов, для которых требуется волновое согласование.

7. Общее число сигнальных слоев должно обеспечить отвод всех сигналов от посадочного места типа BGA с 336 Pad и шагом выводов 0,65 мм.

8. В проекте следует использовать только один тип переходных отверстий — сквозные.

9. Подвод проводников к Pad малых следует производить только от центра наружу, исключение допускается только для элементов, где рекомендованная топология подразумевает иное.

10. Необходимо обеспечить рекомендуемое снижение ширины проводников при подводе к Pad компонентов SMD.

11. Подвод элементов топологии к Pad штыревых компонентов осуществлять только с внутренних слоев.

12. Толщина печатной платы должна равняться 1,6 ±0,1 мм.

Стек слоев

Сначала определим структуру стека слоев. Самым сложным элементом в нашем примере будет корпус BGA с 336 Pad и шагом выводов 0,65 мм. Именно он определит структуру слоев печатной платы и их минимальное число. Поэтому следует изучить рекомендации производителя и максимально им следовать.

Рис. 1. Рекомендуемый PCB Stackup

На рис. 1 показана рекомендуемая разработчиком микросхемы [1] структура слоев для данного посадочного места. Предлагается иметь 8 слоев, из них 4 сигнальных. Кроме того, предлагается использование для перехода с внешних слоев наближний внутренний слой. Общая толщина платы при этом 0,8 мм. Очевидно, что отказ и топологии на внешних слоях требует добавления как минимум двух дополнительных слоев. Так как предполагаемая толщина печатной платы в примере в 2 раза больше рекомендуемой, это дополнительно наложит ограничение на минимальный диаметр сверления для переходного отверстия, что также снизит эффективность использования сигнальных слоев. Более того, с учетом выделения одного слоя для дифференциальных сигналов следовало бы остановиться на числе слоев 12 или 14. Однако в данном примере мы ограничимся числом 10 и при использовании ручной трассировки постараемся всю топологию разместить на таком числе слоев.

Основные требования к конструкции печатных плат указаны в стандарте [2]. Но нужно учитывать и реальные возможности производителей печатных плат. Как правило, они предоставляют на своих сайтах всю информацию об используемых материалах, возможностях производства и требованиях, которые следует соблюдать при проектировании многослойных печатных плат. В нашем примере будем ориентироваться на производство плат в «ПСБ Технолоджи» по одной причине: их требования к материалам печатных плат изложены в одном из номеров данного журнала [3].

Выбор конструкции печатной платы

В соответствии с рекомендацией [3] выберем наиболее распространенный вариант, когда внутренние слои платы формируются из двустороннего ламинированного медью стеклотекстолита («ядро», или core), а наружные слои выполняются из медной фольги, спрессованной с внутренними слоями при помощи связующего смолистого материала (препрег), как показано на рис. 2.

Рис. 2. Конструкция печатной платы

В качестве «ядра» используем наиболее распространенный материал — стандартный стеклотекстолит типа FR4. «Ядра» многослойной печатной платы в нашем примере образуют только внутренние слои. Выберем из стандартного и доступного набора стеклотекстолита у производителя значение толщины «ядра» 0,200 мм, а толщину фольги — 35 мкм (рис. 3). Последняя величина желаема для слоев типа Plane, поскольку в примере будут использованы компоненты с высоким потреблением мощности. Для изготовителя печатных плат такой подход предпочтителен и для сигнальных слоев, поэтому такую толщину фольги оставим для всех внутренних слоев.

Рис. 3. Выбор «ядра» и препрега

Для препрега также используем наиболее распространенную толщину 105 мкм. На внешних слоях выберем толщину медной фольги 17 мкм.

Теперь у нас все готово к созданию непосредственно стека слоев уже в самом пакете проектирования Altium Designer.

Итак, создадим новый проект и в нем новый Данные действия подробно описаны в [4]. Создание нового было продемонстрировано в [5].

Рис. 4. Параметры Layer Stack

Командой Design>>Layer Stack Manager открываем окно задания свойств Layer Stack (рис. 4), где в соответствии с выработанными нами требованиями выбираем следующие свойства:

1. Для добавления слоя печатной платы и установки их типа и порядка следования используем соответствующие кнопки и меню с правой стороны окна. В частности, для нашего случая, когда «ядра» располагаются внутри стека слоев печатной платы (рис. 2), следует выбрать тип Internal Layer Pair.

2. Определим следующие слои, начиная с нижнего:

– 1_Bottom — нижний слой с толщиной фольги 17 мкм;

– 2_OverBottom_forDiffPair — внутренний сигнальный слой с толщиной фольги 35 мкм. Будем их использовать только для дифференциальных пар;

Примечание. Далее все внутренние слои устанавливаем с толщиной фольги 35 мкм.

– 3_Ground_Bottom — слой типа Plane для шины «земля»;

– 4_Mid — сигнальный слой;

– 5_Splitted_VCC — слой типа Plane для шин дополнительных уровней питания;

– 6_Mid_VCC — слой типа Plane для шин основного уровня питания;

– 7_Mid — сигнальный слой;

– 8_Ground_Top — слой типа Plane для шины «земля»;

– 9_underTop — сигнальный слой;

– 10_Top — верхний слой (слой расположения компонентов) с толщиной фольги 17 мкм.

3. Для установки толщины фольги следует сделать двойной клик левой кнопкой указателя по соответствующей надписи с именем слоя (на рисунке это слой 1_Bottom) и ввести нужное значение в открывшемся окне.

4. Для слоев типа Plane в данном окне следует указать также величину PullBack — зазор между Board Outline (контуром печатной платы) и слоем меди. Данный зазор требуется, чтобы при механической обработке контура не было «задира» фольги данного слоя и вообще выхода ее на край печатной платы. В [6] рекомендуют, чтобы данные зазоры в зависимости от сложности производства были не менее:

– упрощенный вариант — 0,50 мм;

– стандартный вариант — 0,25 мм;

– усложненный вариант — 0,2 мм.

Не будем стремиться сделать нашу плату дороже, тем более что для слоев типа Plane, как правило, нет большой необходимости использовать область у края печатной платы. Установим данный зазор равным 0,635 мм.

5. Обратимся к параметрам свойств защитного покрытия платы — маски. Двойной клик левой кнопкой указателя по кнопке «…» для слоя маски Bottom Dielectric вызывает окно, где устанавливаются толщина покрытия маской (в нашем примере 17 мкм) и ее диэлектрическая проницаемость. В [6] приведено значение диэлектрической проницаемости для защитной маски — 4,4. Отметим, что у разных производителей в зависимости от технологии и применяемого покрытия могут быть разные как толщина покрытия маской, так и ее диэлектрическая проницаемость. Поэтому эти величины следует всегда выяснять у производителя печатных плат до начала проектирования многослойной печатной платы, так как их принимают во внимание при расчете зазора и толщины дорожек для скоростных и дифференциальных линий (учет волнового сопротивления).

6. Аналогично поступаем со свойствами Core («ядра»). Здесь устанавливаем рассчитанную толщину — 0,2 мм. В [6] приведены диэлектрические свойства стеклотекстолита FR4 от 4,4 до 4,8. Конкретное значение следует выяснить непосредственно у производителя. Мы установим это значение равным 4,4.

7. Диэлектрические свойства препрега практически такие же, как у стеклотекстолита FR4, и устанавливаются аналогично. Суммарная толщина печатной платы составила 1,67 мм, что лежит в допуске для выбранной категории плат [6] (допуск на толщину готовой многослойной платы не может быть менее ±10%).

8. Установим параметры для переходных отверстий (рис. 5). Кнопка Configure Drill Pair. В данном примере мы ограничимся одним типом переходных отверстий — только сквозными. Поэтому в данном окне присутствует лишь одна запись с указанием верхнего и нижнего слоя.

Рис. 5. Layer Stack. Параметры для переходных отверстий и расчета импеданса

9. Так как в нашем примере приведены дифференциальные линии, можно использовать формулы, встроенные в Altium Designer, для расчета импеданса, а также ширины дорожек. Однако вы вправе изменить формулы расчета и применить рекомендуемые производителем [7] печатных плат или из других достоверных источников.

10. Итак, параметры Layer Stack заданы, и теперь, нажав кнопку “Place Layer Stack Legend”, размещаем сведения о стеке слоев на одном из механических, например, в нашем случае на слое “3_Note”.

11. Для того чтобы информация о Layer Stack перемещалась на PCB как единое целое, выделим все элементы, принадлежащие Layer Stack, и командой (правый клик указателя>>Union >> Create Union From Selected Object) объединим их все в один модуль.

Теперь стек слоев нами задан, а информация о нем размещена на PCB, и мы можем приступать к написанию общих правил для слоев.

Правила учета технологических параметров

В данной статье будут сформулированы только правила, которые определяются технологией производства и классом печатныхплат, а также выбранным типом Layer Stack и переходных отверстий. В [5] было описано назначение правил и даны их типовые примеры. Теперь приведем примеры правил для многослойных печатных плат. Будет дан текст правил, но без указания их приоритета. Приоритет — это важный параметр, и в каждом конкретном случае следует обязательно указывать порядок применения правил. Однако к этому вопросу мы вернемся в отдельном разделе. Для задания свойств правил нам необходима таблица технологических параметров, которую мы заимствуем из [6]. В том порядке, как они указаны в таблице, мы их и приведем. Только единицей представления величин размеров выберем mil, так как до сих пор многие производители печатных плат предпочитают именно ее.

Таблица. Параметры производства плат компании «ПСБ Технолоджи»

1. Число слоев указано в Layer Stack и в правилах не проверяется.

2. Задание ширины проводников по умолчанию. Правило будет действовать на все проводники для всех слоев, если иное не разрешено правилами с более высоким приоритетом. Так как плата у нас содержит 10 слоев и мы будем иметь достаточно плотную трассировку, зададим ширину проводников по умолчанию — минимальное значение 4 mil, типовое значение 5 mil, максимальное 6 mil, что соответствует стандартной сложности.

Правило будет выглядеть так:

– раздел правил Routing/Width;

– имя (Name) правила — Width_All (имя правила определяет разработчик исходя из своих привычек);

– первое (The First Object) условие — All; для всех проводников;

– параметры: Min Width = 4 mil; Preferred Width = 5 mil; Max Width = 6 mil. Минимальная, предлагаемая по умолчанию и максимальная ширина проводника.

Далее мы не будем повторять описание ранее использованных правил и параметров, а приведем их только для новых.

3. Задание зазоров (≥0,1 мм) между проводниками по умолчанию:

– раздел правил Electrical/Clearance;

– имя правила — Clearance_All_to_All;

– первое условие — All (для всех объектов на любом слое);

– второе (The Second Object) условие — All;

– параметры: Different Net Only — для разноименных цепей; Minimum Clearance = = 4 mil.

4. Задание гарантированного «пояска» металлизированного отверстия. Здесь создадим

2 правила: для переходных отверстий с требованием (≥0,15 мм), для отверстий компонентов со штыревыми выводами сделаем больший зазор (≥0,2 мм):

– раздел правил Manufacturing/Minimum Annular Ring;

– имя правила— MinimumAnnularRingForVia;

– первое условие — IsVia (для всех переходных отверстий);

– параметры: Minimum Annular Ring (x–y) = 6 mil;

– имя правила— MinimumAnnularRingForPad;

– первое условие — IsPad (для всех контактных площадок);

Minimum Annular Ring (x–y) = 8 mil.

5. Задание диаметра сквозного отверстия.

Здесь создадим два правила: одно для переходных отверстий, диаметр которых должен быть не менее 0,15 мм; второе для отверстий компонентов со штыревыми выводами, для которых диаметр отверстия внутри контактной площадки должен быть не менее 0,75 мм. В этих правилах ограничим и максимальные значения:

– раздел правил Manufacturing/Hole Size;

– имя правила — HoleSizeForVia;

– первое условие — IsVia (для всех переходных отверстий);

– параметры: Minimum = 6 mil;

Maximum = 40 mil;

– имя правила — HoleSizeForPad;

– первое условие — IsPad (для всех переходных отверстий);

– параметры: Minimum = 30 mil; Maximum = 120 mil.

6. Минимальная площадка сквозного перехода (≥0,45 мм). Здесь же укажем и типовое, и максимальное значения. В этом правиле задается и диаметр переходного отверстия. Сейчас определим только переходные отверстия, используемые по умолчанию.

– раздел правил Routing/Routing Via Style;

– имя правила — RoutingViasDefault;

– первое условие — IsVia (для всех переходных отверстий);

– параметры: Via Diameter, Minimum = = 18 mil, Preferred = 22 mil, Maximum = = 34 mil; Via Diameter, Minimum = 6 mil, Preferred = 8 mil, Maximum = 10 mil.

7. Зазор от отверстия до металла в слоях МПП

(≥0,35 мм):

– раздел правил Electrical/Clearance;

– имя правила — Clearance_All_to_Hole;

– первое условие — All;

– второе условие — HoleSize;

– параметры: Different Net Only; Minimum Clearance = 14 mil.

8. Отношение толщины печатной платы к диаметру переходного отверстия 10:1. Здесь правило не пишется. Просто рассчитаем диаметр минимального отверстия как десятую часть от толщины платы, что составит 0,167 мм. Как видно, данная величина превышает значение в пункте 5. Нам следует вернуться к правилам HoleSizeForVia и увеличить значение параметра Minimum до величины 6,5 mil или известить производителя о другом допуске.

9. Зазор от металла до края ПП. Как правило, под этим понимают большее — это зазор не только до края печатной платы, но и до любых вырезов в ней и других объектов, требующих запрета топологии. Обычно такие зоны запрета указываются в слое KeepOut. Здесь тоже зададим два правила: одно общее, другое для наружных слоев с увеличенным зазором 0,635 мм для гарантированного зазора с возможным контактом с механическими направляющими, держателями, планками и т. п.:

– раздел правил Electrical/Clearance;

– имя первого правила— Clearance_to_Keep-Out;

– первое условие — ALL;

– второе условие Layer’) (для всего на слое Keep-Out);

– параметры: Any Net — для любых цепей; Minimum Clearance = 20 mil;

– имя второго правила— Clearance_OnOutside_Keep-Out;

– первое условие — OnOutside (для всего на внешних слоях);

– второе условие — OnLayer Layer’);

– параметры: Any Net; Minimum Clearance = 25 mil.

10. Зазор от края отверстия до края ПП (≥0,45 мм):

– раздел правил Electrical/Clearance;

– имя правила— Clearance_KeepOut_To_Hole;

– первое условие — OnLayer Layer’);

– второе условие — HoleSize;

– параметры: Any Net; Minimum Clearance = 16 mil.

11. Зазор от площадки до маски (≥0,075 мм).

– раздел правил Mask/Solder Mask Expansion;

– имя правила — SolderMaskExpansion;

– первое условие — All;

– параметры: Expansion = 3 mil.

12. То же касается и минимальной полоски маски.

13. Правил для «глухих» отверстий создавать не будем, так как в этом примере мы их не используем.

Итак, правила, контролирующие технологические возможности производителя, приведены. Теперь рассмотрим другие аспекты при разработке многослойных плат и сложных проектов.

Все остальные правила по возможности будем указывать непосредственно на схеме, так как именно разработчик схемы должен определять ключевые вопросы топологии для наиболее важных и критичных электрических связей.

Правила для контроля общих требований к печатной плате

Здесь укажем типовые правила для обеспечения как надежности изготовления многослойной печатной платы, так и повышения качества монтажа компонентов на печатной плате.

1. Установим зазор между площадками Pad и другими элементами топологии не менее 0,15 мм. Это правило более важное, чем правило из пункта 3 предыдущего раздела (правило для зазоров ≥0,1 мм между проводниками по умолчанию), и оно должно обладать более высоким приоритетом. Связано это с тем, что Pad не закрыты маской, и, вследствие этого, края проводников элементов топологии вблизи Pad могут быть открыты, что при монтаже может вызвать замыкание. Правило будет таким:

– раздел правил Electrical/Clearance;

– имя правила — Clearance_To_Pad;

– первое условие — IsPad;

– второе условие — All;

– параметры: Different Net Only; Minimum Clearance = 6 mil.

2. В случае если переходные отверстия не закрываются маской, аналогичное правило можно написать и для Via, или включить в первое условие предыдущего правила IsPad or Via.

3. Для гарантированного запрета «утекания» припоя в переходное отверстие для SMDкомпонентов зададим минимальный зазор от Pad до Via не менее 0,2 мм:

– раздел правил Electrical/Clearance;

– первое условие — IsPad;

– второе условие — IsVia;

– параметры: Same Net Only; Minimum Clearance = 8 mil. Правило действует для Pad и Via, принадлежащих одной электрической цепи.

4. Так как пока классов цепей у нас нет, сделаем только одно правило для типа топологии:

– раздел правил Routing/Routing Topology;

– имя правила — RoutinTopology;

– первое условие — All;

– параметры: Topology = Daisy-Simple.

5. Определим слои, доступные для топологии всех электрических цепей, и отдельно для дифференциальных линий (в нашем случае их два: верхний слой, где расположены компоненты, и специально отведенный внутренний слой). Правила выглядят так:

– раздел правил Routing/Routing Layer;

– имя первого правила — RoutingLayers;

– первое условие — All;

– параметры: Enable Layer = 10_Top, 9_underTop, 7_Mid, 4_Mid;

– имя второго правила— RoutingLayers_Diff;

– первое условие — InAnyDifferentialPair;

– параметры: Enable Layer = 10_Top, 2_OverBottom_forDiffPair.

6. Для запрета подключения проводников под острым углом (кроме дифференциальных линий) добавим следующее правило:

– раздел правил SMT/SMD to Corner;

– первое условие — Not InAnyDifferentialPair;

– параметры: Distance = 4 mil.

7. Для улучшенного термопрофиля при пайке обеспечим, чтобы ширина подходящих к Pad проводников была меньше ширины самого Pad:

– раздел правил SMT/SMD Neck-Down;

– первое условие — IsSMTPin;

8. Зазор от площадки до маски (≥0,075 мм).

– раздел правил Mask/Solder Mask Expansion;

– имя правила — SolderMaskExpansion;

– первое условие — All;

– параметры: Expansion = 3 mil.

9. Зазор маски для нанесения паяльной пасты сделаем нулевым:

– раздел правил Mask/Paste Mask Expansion;

– имя правила — PasteMaskExpansion;

– первое условие — All;

– параметры: Expansion = 0 mil.

10. Теперь укажем правила для заливки слоев Plane. Здесь установим три правила: для подключения к переходным отверстиям, к Pad штыревых компонентов с малым и большим значением диаметра Hole:

– раздел правил Plane/Power Plane Connect Style;

– имя правила — PlaneConnect;

– первое условие — All;

– параметры: Connect Style = Relief Connect (термобарьер); Conductor = 4 (число подводящих проводников); Conductor Width = 7 mil (ширина проводников); = 3 mil (зазор для термобарьера); Expansion = 6 mil («поясок» для отверстия в слое Plane);

– имя правила — PlaneConnect_Via;

– первое условие — IsVia;

– параметры: Connect Style = Direct Connect. Подключение к переходным отверстиям в слое Plane без термобарьеров;

– имя правила — PlaneConnect_BigHole;

– первое условие — (ObjectKind = ‘Pad’) And (HoleDiameter >= ’50’) (для всех отверстий с диаметром больше 50 mil);

– параметры: Connect Style = Relief Connect; Conductor = 4; Conductor Width = 12 mil; = 6 mil; Expansion = 20.

11. Зададим правила подключения полигонов:

– раздел правил Plane/Polygon Connect Style;

– имя правила — PolygonConnect (правило подключения полигонов по умолчанию);

– первое условие — All;

– второе условие — All;

– параметры: Connect Style = Relief Connect (термобарьер); Conductor = 4, 45 Angle (четыре подводящих проводника под углом 45°); Conductor Width = = 5 mil (ширина проводников) (Примечание. Обратите внимание, в отличие от слоя типа Plane в этом правиле зазор для термобарьера не задается! Для этого есть отдельные правила из раздела Clearance.);

– имя правила — PolygonConnect_to_Via (правило подключения полигонов к переходным отверстиям; здесь разрешим сплошную заливку полигона);

– первое условие — All;

– второе условие — IsVia;

– параметры: Connect Style = Direct Connect (без термобарьера);

– имя правила— PolygonConnect_TOPandBOTforPad (правило подключения полигонов к Pad на внешних сторонах платы; для сохранения одинакового термопрофиля при пайке запретим подключение любых полигонов к Pad);

– первое условие — OnOutside;

– второе условие — IsPad;

– параметры: Connect Style = No Connect.

12. Правила для запрета острых углов между проводниками. Здесь приведем три правила:

– раздел правил Manufacturing/Acute Angle;

– имя правила — AcuteAngle (по умолчанию);

– первое условие — All;

– второе условие — All;

– параметры: Minimum Angle = 89.999;

– имя правила — AcuteAngle_Diff (для дифференциальных линий минимальный угол — 135°);

– первое условие — InAnyDifferentialPair;

– второе условие — InAnyDifferentialPair;

– параметры: Minimum Angle = 134.999;

– имя правила — AcuteAngle_SplitPlanes (для линий — разделяющих 5−й слой Plane на зоны; этот слой предназначен для нескольких уровней питания);

– первое условие — OnLayer (‘5_Splitted_VCC’);

– второе условие — OnLayer (‘5_Splitted_VCC’);

– параметры: Minimum Angle = 134.999.

13. Ограничим длину рядом идущих проводников:

– раздел правил High Speed/Parallel Segment;

– имя правила— ParallelSegmentOnSameLayer;

– первое условие — All;

– второе условие — All;

– параметры: Layer Checking = Same Layer (для проводников в одном слое); For parallel gap of = 10 mil (на расстоянии друг от друга до указанной величины); The parallel limit is = 1000 mil (допускается указанная величина параллельных проводников);

– имя правила— ParallelSegmentOnAdjacentLayer;

– первое условие — All;

– второе условие — All;

– параметры: Layer Checking = Same Layer (для проводников в смежных слоях); For parallel gap of = 6 mil; The parallel limit is = 1000 mil.

14. Ограничим максимальную длину проводника:

– раздел правил High Speed/Length;

– имя правила — Length;

– первое условие — All;

– параметры: Minimum = 3 mil; Maximum = 10 000 mil.

15. Определим максимальную длину отвода от проводника:

– раздел правил High Speed/StubLength;

– имя правила — StubLength (по умолчанию);

– первое условие — All;

– параметры: Maximum StubLength = 1000 mil;

– имя правила — StubLengthDiff (для дифференциальных линий);

– первое условие — All;

– параметры: Maximum StubLength = 75 mil.

16. Запретим установку переходных отверстий на Pad SMD-компонентов:

– раздел правил High Speed/Vias Under SMD;

– имя правила — Vias Under SMD;

– первое условие — All;

– параметры: Vias Under SMD Pads = флаг снят.

17. Установим максимальное число переходных отверстий для одного проводника:

– раздел правил High Speed/Maximum Via Cont;

– имя правила — MaximumViaCont;

– первое условие — All;

– параметры: Maximum Via Cont = 10.

18. Укажем зазор для установки компонентов:

– раздел правил Placement/Component Clearance;

– имя правила — ComponentClearance;

– первое условие — All;

– второе условие — All;

– параметры: Vertical ClearanceMode = = Specified (установлена и проверка по высоте компонентов); Minimum Horizontal Clearance = 20 mil; Minimum Vertical Clearance = 50 mil.

19. Укажем сторону размещения компонентов:

– раздел правил Placement/Permitted Layers;

– имя правила — PermittedLayers;

– первое условие — All;

– параметры: Permitted Layers = Top Layer.

Итак, типовые правила для нашего проекта созданы, и мы можем приступать к разработке схемы и топологии. Отметим, что основная масса правил формулируется для готового проекта, когда схема уже создана. Далее при рассмотрении проекта мы не будем приводить подробное описание правила (кроме сложных случаев с точки зрения построения выражений), укажем лишь их параметры. Более того, при возможности будем эти правила описывать непосредственно в схемном редакторе.

Литература

1. PXA27x Processor Family Design Guide.pdf // www.intel.com

2. IPC_2221. Generic Standard on Printed Board Design.

3. Акулин А. И. Проектирование многослойных печатных плат. Журнал в журнале // Технологии в электронной промышленности. 2006. № 6.

4. Пранович В. Система проектирования Altium Designer 6 // Технологии в электронной промышленности. 2007. № 1.

5. Пранович В. Altium Designer 6 в примерах // Технологии в электронной промышленности. 2007. № 5–8.

6. Акулин А. И. Технологические параметры многослойных печатных плат и критерии их выбора // Технологии в электронной промышленности. 2007. № 5.

7. Акулин А. И. Целостность сигналов на печатной плате и волновое сопротивление проводников // Технологии в электронной промышленности. 2007. № 1.

Создание и настройка проектов. Настройка панелей. Создание Design Workspace. Создание нового проекта. Создание нового документа в проекте. Создание библиотек PCB Library. Создание библиотек Schematic Library. Создание библиотек Int Library. Создание листа новой схемы в проекте. Внесение в проект элементов схемы. Присвоение позиционных номеров компонентам схемы. Выбор и изменение модели Footprint-компонента. Завершение формирования схемы.

Топология идентичных блоков модуля. Реализация типовых схемных и топологических решений в примере. Использование полигонов. Подготовка и размещение текстовой и пояснительной информации на печатной плате.

Подготовка файлов для изготовления печатных плат. Подготовка файлов и документации с помощью Job File. Assembly Drawing из группы настроек Assembly Output. Generates pick and Places File (сведения о координатах компонентов). Gerber Files, NC Drill Files, ODB++ Files. Test Point Report. Группа Report Output Bill off materials. Формирование 3D изображения печатной платы. Формирование PDF файла проекта.

Задание правил топологии в PCB редакторе. Разделы правил Testpoint и Manufacturing. Раздел правил High Speed. Разделы правил Placement. Расстановка компонентов. Создание Room из компонентов. Создание Union.