Набор команд процессоров Intel® AVX-512 (Advanced Vector Extensions 512).

Набор команд процессоров Intel® AVX-512 (Advanced Vector Extensions 512).

В различных отраслях продолжает возрастать потребность в повышенной вычислительной мощности. Чтобы поддержать повышающийся спрос и усложняющиеся модели использования, продолжается предоставка оптимизированных под рабочие нагрузки инновационных решений, реализуемых в наборе команд Intel® AVX-512, которым оснащены новейшие процессоры и сопроцессоры Intel® Xeon Phi™1, а такжемасштабируемые процессоры Intel® Xeon® .

Intel® AVX-512 — это новый набор команд, который повышает производительность различных рабочих нагрузок, включая научное моделирование, финансовую аналитику, искусственный интеллект и глубинное обучение, 3D-моделирование и анализ данных, обработку изображений, аудио и видео, сжатие данных и шифрование.

Набор инструкций AVX-512 состоит из нескольких отдельных наборов, каждый из которых имеет свой собственный уникальный бит функции CPUID; однако их обычно группируют, поддерживая генерацию процессора ( F, CD, ER, PF, BW, DQ, VL, IFMA, VBMI 4VNNIW, 4FMAPS … см. табл.1) .

AVX-512 состоит из нескольких расширений, которые не все должны поддерживаться всеми реализующими их процессорами. Во всех реализациях требуется только базовое расширение AVX-512F (AVX-512 Foundation).

Использование AVX-512 будет означать, что обработка массивных мультимедийных данных будет проходить с меньшей нагрузкой на процессор. Точнее, работа с использованием аппаратных ресурсов, совместимых с AVX-512, будет максимально эффективна. На этих задачах потребление снизится, а производительность вырастет.

Таблица 1. Процессоры с AVX-512

Появляются усовершенствованные возможности векторной обработки. Благодаря возможностям для осуществления операций с 512-битными векторами набор команд Intel® AVX-512 справится даже с наиболее требовательными вычислительными задачами.

Приложения могут осуществлять 32 операции с плавающей запятой в секунду с удвоенной точностью и 64 операции с плавающей запятой в секунду с одинарной точностью за тактовый цикл в 512-битных векторах, а также 8 целочисленных типов шириной 64 бит и 16 целочисленных типов шириной 32 бит и до двух 512-битных команд Fused Multiply-Add (FMA). Таким образом, ширина регистров данных, число регистров и ширина команд FMA вдвое больше по сравнению с набором команд Intel® Advanced Vector Extensions 2.0 (Intel® AVX2). Можно значительно повысить производительность с помощью набора команд Intel® AVX-512. Intel® Advanced Vector Extensions 512, новейший набор векторных команд x86, включает в себя до двух команд FMA (Fused Multiply-Add) и другие оптимизации для повышения производительности наиболее ресурсоемких вычислительных задач.

Intel® AVX 2.0 позволяет выполнять 16 операций с плавающей запятой в секунду с удвоенной точностью и 32 операции с плавающей запятой в секунду с одинарной точностью за тактовый цикл в 256-битных векторах, а также до двух 256-битных команд Fused Multiply-Add (FMA).

Intel заставляет производителей матплат отключать поддержку AVX-512

Блоки векторных инструкций AVX-512 на процессоре Core i9-12900K

Всем производителям материнских плат Z690 на процессорах Alder Lake пришло обновление микрокода от Intel, которое полностью запрещает использование инструкций AVX-512.

Физически модуль AVX-512 остался на ядрах P. Его можно было активировать через BIOS и повысить производительность в 14–32 раза в некоторых специфических задачах, отключив при этом малополезные ядра E. Теперь лазейку закрыли.

Таким образом Intel окончательно убрала официальную поддержку AVX-512 из новых процессоров 12-го поколения Alder Lake. Изначально предполагалось, что этот модуль физически убрали с микросхемы, потому что он занимает много места. Но потом выяснилось, что блоки остались на месте, но только в производительных ядрах P.

Обновление микрокода пришло производителям буквально за несколько дней до начала выставки CES 2022, где Intel собирается представить ряд младших процессоров в семействе Alder Lake. Естественно, все они работают на материнских платах с чипсетом Z690. И вот теперь компания решила окончательно закрыть вопрос с поддержкой AVX-512.

Набор инструкций AVX-512 расширяет систему команд AVX до векторов длиной 512 бит при помощи кодировки с префиксом EVEX. Расширение AVX-512 вводит 32 векторных регистра (ZMM), каждый по 512 бит, 8 регистров масок, 512-разрядные упакованные форматы для целых и дробных чисел и операции над ними, тонкое управление режимами округления (позволяет переопределить глобальные настройки), операции broadcast (рассылка информации из одного элемента регистра в другие), подавление ошибок в операциях с дробными числами, операции gather/scatter (сборка и рассылка элементов векторного регистра в/из нескольких адресов памяти), быстрые математические операции, компактное кодирование больших смещений. Блок AVX-512 реализован в следующих процессорах: Intel Xeon Phi x200 и x205 (в сопроцессорах Knights Landing и Knights Mill), а также в семействах Skylake-SP, Skylake-X, Cannon Lake, Cascade Lake, Cooper Lake, Ice Lake, Rocket Lake, Tiger Lake, Sapphire Rapids.

Причины отключения AVX-512

Официально причины не разглашаются. Мы можем только предполагать. Дело в том, что единственным условием для активации AVX-512 является отключение ядер E. При этом во многих задачах такая замена (AVX-512 вместо ядер E) практически не отражается на производительности или даже улучшает её.

Отключение ядер E практически не отражается на производительности после активации AVX-512

Другая причина: усложнение настроек с отключением/включением ядер создаёт дополнительную нагрузку на службу технической поддержки Intel.

Наконец, самое главное. Программное отключение AVX-512 в десктопных процессорах создаёт дополнительный спрос на процессоры для рабочих станций и серверов, где набор инструкций будет работать как положено. В данном случае компании совершенно не нужно, чтобы коммерческие клиенты использовали более дешёвые настольные процессоры.

В проигрыше остаются пользователи, которые хотели воспользоваться преимуществами AVX-512 именно на последнем поколении настольных процессоров Intel. Теперь им остаётся использовать другие процессоры с поддержкой AVX-512, то есть все предыдущие поколения Intel или будущее поколение AMD Ryzen, которое выйдет очень скоро.

Искусственная рыночная сегментация и распределение пользователей по секторам рынка с разной рентабельностью — известный приём, который позволяет максимизировать прибыль. Им пользуются очень многие компании, которые выпускают примерно одинаковые товары, но для разных рыночных сегментов и по разным ценам.

Intel многократно использовала этот приём. Говорят, в первых семи поколениях Core специально не выпускались настольные процессоры более чем с четырьмя ядрами, чтобы не повредить более прибыльному серверному сегменту.

Выпуск одинаковых процессоров в «залоченной» и «разлоченной» версиях, с отключенными/включенными ядрами и т. д. — это стандартный арсенал грязных приёмов у производителей компьютерных комплектующих.

Ограничения на AVX2

Проблема с блокировкой AVX-512 усугубляется тем, что в оставшемся наборе инструкций AVX2 стоит ограничение на максимальный множитель тактовой частоты х51, пишет Igor’s Lab.

То есть при выполнении инструкций AVX2 тактовая частота процессора принудительно понижается до 5,1 ГГц не может быть поднята даже до 5,2 ГГц ни при каких настройках BIOS, независимо от охлаждения, энергопотребления, реальной температуры CPU или запущенного приложения. Например, в программе HWInfo режим принудительного ограничения частоты можно распознать по строке IA: Max Turbo Limit – Yes .

Активирован режим IA: Max Turbo Limit – Yes

Неофициальные хаки

К счастью, уже разработаны методы обхода программных ограничений, установленных Intel, как в отношении блокировки AVX-512, так и по троттлингу AVX2.

Например, компания Asus в материнских платах серии Maximus реализовала патч BIOS, который отключает троттлинг AVX2 при условии принудительного выставления тактовой частоты в BIOS.

Активировать AVX-512 сложнее, но тоже возможно. Сообщество уже нашло способ внедрить в новую прошивку старую версию микрокода от Intel, что эффективно включает обратно AVX-512.

Конечно, в этом случае мы получаем неофициальную версию BIOS с лишением гарантии и всеми вытекающими последствиями. Но это хотя бы доказывает, то отключение AVX-512 является обратимым.

- Блог компании ITSumma

- Производство и разработка электроники

- Компьютерное железо

- Настольные компьютеры

- Процессоры

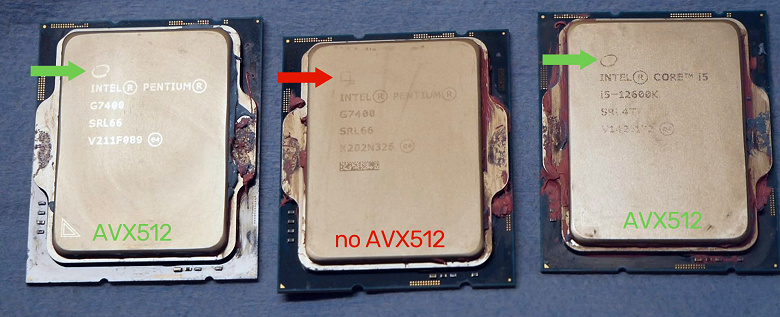

Знак на крышке процессора Intel позволит отличить модели с огромным скрытым потенциалом. Стало известно, как определить CPU с поддержкой AVX-512

В Сети описали способ, как быстро визуально отличить процессор Intel Alder Lake с поддержкой инструкций AVX-512 от версии без такой поддержки.

Как оказалось, у новой ревизии на крышке новый логотип. Сначала некоторые пользователи даже думали, что это поддельные CPU, но тут никаких проблем нет.

Процессоры новой ревизии с новым логотипом как раз не имеют поддержки AVX-512 на аппаратном уровне. Intel начала поставлять такие CPU в марте, так что, скорее всего, встретить старую ревизию в продаже будет уже не так просто, но вероятность всё равно имеется.

Напомним, CPU Alder Lake изначально вышли с поддержкой инструкций AVX-512, хотя Intel официально сначала ничего об этом не говорила. Позже компания выпустила обновление BIOS для системных плат, которое блокирует такой режим работы, а с начала весны начала поставлять уже новую ревизию, где поддержка этих инструкций отсутствует уже на аппаратном уровне.

Поддержка AVX-512 нужна далеко не всем, но в ряде приложений в таком режиме этот набор инструкций делает процессор в два-три раза производительнее, но за это придётся заплатить сильно возросшим энергопотреблением.

AVX-512

AVX-512 — это 512-битные расширения для 256-битных инструкций SIMD Advanced Vector Extensions для архитектуры набора команд x86 (ISA), предложенные Intel в июле 2013 года и реализованные в Intel Xeon Phi x200 (Knights Landing) [1] и Skylake- X процессоров; это включает в себя серию Core-X (за исключением Core i5-7640X и Core i7-7740X), а также новое семейство масштабируемых процессоров Xeon и Xeon D-2100 Embedded. [2]

AVX-512 — не первый 512-битный набор инструкций SIMD, который Intel представила в процессорах: более ранние 512-битные инструкции SIMD, используемые в сопроцессорах Xeon Phi первого поколения , унаследованные от проекта Intel Larrabee , похожи, но не совместимы с двоичным кодом и только частично совместим с исходным кодом. [1]

AVX-512 состоит из нескольких расширений, которые могут быть реализованы независимо. Эта политика является отходом от исторического требования реализации всего блока инструкций. Для всех реализаций AVX-512 требуется только базовое расширение AVX-512F (AVX-512 Foundation).

- 1 набор инструкций

- 2 Кодировка и особенности

- 2.1 Режимы SIMD

- 2.2 Расширенные регистры

- 3.1 Новые инструкции opmask

- 4.1 Смешивание с использованием маски

- 4.2 Сравнить в маске

- 4.3 Маска логического набора

- 4.4 Сжимать и расширять

- 4.5 Перестановка

- 4.6 Побитовая троичная логика

- 4.7 Конверсии

- 4.8 Разложение с плавающей запятой

- 4.9 Арифметика с плавающей запятой

- 4.10 Трансляция

- 4.11 Разное

- 5.1 Обнаружение конфликтов

- 5.2 Экспоненциальный и обратный

- 5.3 Предварительная выборка

- 5.4 4FMAPS и 4VNNIW

- 5.5 BW, DQ и VBMI

- 5.5.1 Инструкции с плавающей запятой

- 5.5.2 Прочие инструкции

Набор инструкций [ править ]

Набор команд AVX-512 состоит из нескольких отдельных наборов, каждый из которых имеет свой уникальный бит функции CPUID; однако они обычно группируются по поколению процессоров, в котором они реализованы.

- AVX-512 Foundation (F) — расширяет большинство 32-битных и 64-битных инструкций AVX схемой кодирования EVEX для поддержки 512-битных регистров, масок операций, широковещательной передачи параметров, а также встроенного управления округлением и исключениями, реализованного Knights Landing и Skylake Xeon

- AVX-512 Инструкции по обнаружению конфликтов (CD) — эффективное обнаружение конфликтов, позволяющее векторизовать больше циклов , реализовано Knights Landing [1] и Skylake X

- AVX-512 Exponential and Reciprocal Instructions (ER) — экспоненциальные и взаимные операции, предназначенные для помощи в реализации трансцендентных операций, реализованные Knights Landing [1]

- AVX-512 Prefetch Instructions (PF) — новые возможности предварительной выборки, реализованные Knights Landing [1]

- AVX-512 Vector Length Extensions (VL) — расширяет большинство операций AVX-512 для работы с регистрами XMM (128-бит) и YMM (256-бит) [3]

- AVX-512 Doubleword and Quadword Instructions (DQ) — добавляет новые 32-битные и 64-битные инструкции AVX-512 [3]

- AVX-512 Byte and Word Instructions (BW) — расширяет AVX-512 для охвата 8-битных и 16-битных целочисленных операций [3]

- AVX-512 Integer Fused Multiply Add (IFMA) — плавное сложение целых чисел с использованием 52-битной точности.

- AVX-512 Vector Byte Manipulation Instructions (VBMI) добавляет команды перестановки векторных байтов, которых не было в AVX-512BW.

- AVX-512 Векторные инструкции нейронной сети Word variable precision (4VNNIW) — векторные инструкции для глубокого обучения, улучшенного слова, переменной точности.

- AVX-512 Fused Multiply Accumulation Packed Single precision (4FMAPS) — векторные инструкции для глубокого обучения, с плавающей запятой, одинарной точности.

- AVX-512 Vector Neural Network Instructions (VNNI) — векторные инструкции для глубокого обучения.

- AVX-512 Vector Byte Manipulation Instructions 2 (VBMI2) — загрузка байта / слова, сохранение и объединение со сдвигом.

- AVX-512 Bit Algorithms (BITALG) — инструкции по манипулированию битами байтов / слов, расширяющие VPOPCNTDQ.

- AVX-512 Пересечение векторной пары с парой регистров маски (VP2INTERSECT) .

- Это не функции AVX-512 как таковые. Вместе с AVX-512 они включают версии инструкций GFNI, PCLMULQDQ и AES в кодировке EVEX .

Кодировка и особенности [ править ]

VEX приставку используется AVX и AVX2, в то время как гибкий, не оставил достаточно места для функций Intel хотел бы добавить к AVX-512. Это привело к созданию нового префикса EVEX .

По сравнению с VEX, EVEX имеет следующие преимущества: [6]

- Расширенное кодирование регистров, позволяющее использовать 32 512-битных регистра.

- Добавляет 8 новых регистров opmask для маскировки большинства инструкций AVX-512.

- Добавляет новый режим скалярной памяти, который автоматически выполняет широковещательную рассылку.

- Добавляет место для явного контроля округления в каждой инструкции.

- Добавляет новый режим адресации сжатой памяти смещения .

Расширенные регистры, бит ширины SIMD и регистры opmask AVX-512 являются обязательными и требуют поддержки со стороны ОС.

Режимы SIMD [ править ]

Инструкции AVX-512 предназначены для смешивания с 128/256-битными инструкциями AVX / AVX2 без потери производительности. Однако расширения AVX-512VL позволяют использовать инструкции AVX-512 в 128/256-битных регистрах XMM / YMM, поэтому большинство инструкций SSE и AVX / AVX2 имеют новые версии AVX-512, закодированные с префиксом EVEX, что обеспечивает доступ к новым функциям. такие как opmask и дополнительные регистры. В отличие от AVX-256, новые инструкции не имеют новой мнемоники, но разделяют пространство имен с AVX, что делает различие между версиями инструкции в кодировке VEX и EVEX неоднозначным в исходном коде. Поскольку AVX-512F работает только с 32- и 64-битными значениями, инструкции SSE и AVX / AVX2, которые работают с байтами или словами, доступны только с расширением AVX-512BW (поддержка байтов и слов). [6]

Имя Наборы удлинителей Регистры Типы Устаревший SSE SSE-SSE4.2 xmm0-xmm15 одиночные поплавки. Из SSE2: байты, слова, двойные слова, четверные слова и двойные числа с плавающей запятой. AVX-128 (VEX) AVX, AVX2 xmm0-xmm15 байты, слова, двойные слова, четверные слова, одиночные числа с плавающей запятой и двойные числа с плавающей запятой. AVX-256 (VEX) AVX, AVX2 ymm0-ymm15 одинарный поплавок и двойной поплавок. Из AVX2: байты, слова, двойные слова, четверные слова AVX-128 (EVEX) AVX-512VL xmm0-xmm31 (k1-k7) двойные слова, четверные слова, одинарное число с плавающей запятой и двойное число с плавающей запятой. С AVX512BW: байты и слова AVX-256 (EVEX) AVX-512VL ymm0-ymm31 (k1-k7) двойные слова, четверные слова, одинарное число с плавающей запятой и двойное число с плавающей запятой. С AVX512BW: байты и слова AVX-512 (EVEX) AVX-512F zmm0-zmm31 (k1-k7) двойные слова, четверные слова, одинарное число с плавающей запятой и двойное число с плавающей запятой. С AVX512BW: байты и слова Расширенные регистры [ править ]

Схема регистров x64 AVX-512 как расширение регистров x64 AVX (YMM0-YMM15) и x64 SSE (XMM0-XMM15)

511 256 255 128 127 0 ZMM0 YMM0 XMM0 ZMM1 YMM1 XMM1 ZMM2 YMM2 XMM2 ZMM3 YMM3 XMM3 ZMM4 YMM4 XMM4 ZMM5 YMM5 XMM5 ZMM6 YMM6 XMM6 ZMM7 YMM7 XMM7 ZMM8 YMM8 XMM8 ZMM9 YMM9 XMM9 ZMM10 YMM10 XMM10 ЗММ11 YMM11 XMM11 ЗММ12 YMM12 XMM12 ZMM13 YMM13 XMM13 ЗММ14 YMM14 XMM14 ZMM15 YMM15 XMM15 ЗММ16 YMM16 XMM16 ЗММ17 YMM17 XMM17 ЗММ18 YMM18 XMM18 ЗММ19 YMM19 XMM19 ZMM20 YMM20 XMM20 ZMM21 YMM21 XMM21 ZMM22 YMM22 XMM22 ZMM23 YMM23 XMM23 ZMM24 YMM24 XMM24 ZMM25 YMM25 XMM25 ZMM26 YMM26 XMM26 ZMM27 YMM27 XMM27 ZMM28 YMM28 XMM28 ZMM29 YMM29 XMM29 ZMM30 YMM30 XMM30 ZMM31 YMM31 XMM31 Ширина файла регистров SIMD увеличена с 256 до 512 бит и расширена с 16 до 32 регистров ZMM0-ZMM31. Эти регистры могут быть адресованы как 256-битные регистры YMM из расширений AVX и 128-битные регистры XMM из потоковых расширений SIMD , а устаревшие инструкции AVX и SSE могут быть расширены для работы с 16 дополнительными регистрами XMM16-XMM31 и YMM16-YMM31 при использовании EVEX. закодированная форма.

Регистры Opmask [ править ]

Большинство инструкций AVX-512 могут указывать на один из 8 регистров opmask (k0 – k7). Для инструкций, которые используют регистр маски в качестве маски операции, регистр k0 является особенным: жестко запрограммированная константа, используемая для обозначения немаскированных операций. Для других операций, таких как те, которые записывают в регистр opmask или выполняют арифметические или логические операции, k0 является действующим действующим регистром. В большинстве инструкций маска операции используется для управления тем, какие значения записываются в место назначения. Флаг управляет поведением opmask, которое может быть либо «нулевым», при котором обнуляется все, что не выбрано маской, либо «слияние», при котором все не выбранное остается нетронутым. Поведение слияния идентично инструкциям по смешиванию.

Регистры opmask обычно имеют ширину 16 бит, но могут иметь длину до 64 бит с расширением AVX-512BW. [6] Однако, сколько битов фактически используется, зависит от типа вектора маскируемых инструкций. Для 32-битных одинарных слов с плавающей запятой или двойных слов 16 бит используются для маскировки 16 элементов в 512-битном регистре. Для двойных слов с плавающей точкой и четверных слов используется не более 8 битов маски.

Регистр opmask — это причина, по которой несколько побитовых инструкций, которые, естественно, не имеют ширины элементов, были добавлены в AVX-512. Например, побитовое И, ИЛИ или 128-битное перемешивание теперь существует как для двойного, так и для четверного слова, с единственной разницей в окончательной маскировке.

Новые инструкции opmask [ править ]

Регистры opmask имеют новое мини-расширение инструкций, работающих непосредственно с ними. В отличие от остальных инструкций AVX-512, все эти инструкции закодированы в VEX. Все начальные инструкции opmask — это 16-битные (Word) версии. С AVX-512DQ были добавлены 8-битные (байтовые) версии, чтобы лучше соответствовать потребностям маскировки 8 64-битных значений, а с AVX-512BW были добавлены 32-битные (Double) и 64-битные (Quad) версии, чтобы они могли маска до 64 8-битных значений. Инструкции KORTEST и KTEST могут использоваться для установки флагов x86 на основе регистров маски, так что их можно использовать вместе с ветвлениями x86, отличными от SIMD, и условными инструкциями.

Инструкция Набор удлинителей Описание KAND F Побитовое логическое И Маски KANDN F Побитовое логическое И НЕ Маски KMOV F Переход от и к регистрам маски или регистрам общего назначения KUNPCK F Распаковать регистры маски KNOT F НЕ Маскирующий регистр KOR F Побитовые логические маски ИЛИ KORTEST F ИЛИ маски и установить флаги KSHIFTL F Сдвиг влево регистры маски KSHIFTR F Сдвиг вправо регистры маски KXNOR F Побитовые логические маски XNOR KXOR F Побитовые логические маски XOR KADD BW / DQ Добавить две маски KTEST BW / DQ Побитовое сравнение и установка флагов Новые инструкции в основах AVX-512 [ править ]

Многие инструкции AVX-512 являются просто версиями EVEX старых инструкций SSE или AVX. Однако есть несколько новых инструкций и старые инструкции, которые были заменены новыми версиями AVX-512. Новые или существенно переработанные инструкции перечислены ниже. Эти базовые инструкции также включают расширения от AVX-512VL и AVX-512BW, поскольку эти расширения просто добавляют новые версии этих инструкций вместо новых инструкций.

Смешайте с помощью маски [ править ]

Версий инструкций смешивания из SSE4 с префиксом EVEX не существует ; вместо этого AVX-512 имеет новый набор инструкций смешивания, использующих регистры маски в качестве селекторов. Вместе с общими инструкциями сравнения с маской, приведенными ниже, они могут использоваться для реализации общих тернарных операций или cmov, подобных VPCMOV XOP .

Поскольку смешивание является неотъемлемой частью кодирования EVEX, эти инструкции также можно рассматривать как базовые инструкции перемещения. Используя режим наложения обнуления, их также можно использовать в качестве инструкций по маскированию.

Инструкция Набор удлинителей Описание VBLENDMPD F Смешивание векторов float64 с помощью opmask control VBLENDMPS F Смешивание векторов float32 с помощью opmask control VPBLENDMD F Смешивание векторов int32 с помощью opmask control VPBLENDMQ F Смешивание векторов int64 с помощью элемента управления opmask VPBLENDMB BW Смешивание байтовых целочисленных векторов с помощью элемента управления opmask VPBLENDMW BW Смешивание целочисленных векторов слов с помощью элемента управления opmask Сравнить с маской [ править ]

AVX-512F имеет четыре новых инструкции сравнения. Как и их аналоги XOP, они используют непосредственное поле для выбора между 8 различными сравнениями. Однако, в отличие от своих идей XOP, они сохраняют результат в регистре маски и изначально поддерживают только сравнения двойных и четверных слов. Расширение AVX-512BW предоставляет версии в байтах и словах. Обратите внимание, что для инструкций могут быть указаны два регистра маски: один для записи, а другой для объявления регулярного маскирования. [6]

Немедленный Сравнение Описание 0 Эквалайзер Равный 1 LT Меньше, чем 2 LE Меньше или равно 3 ЛОЖНЫЙ Установить на ноль 4 NEQ Не равный 5 NLT Больше или равно 6 NLE Больше чем 7 ПРАВДА Установить на один Маска логического набора [ править ]

Последний способ установки масок — использование маски логического набора. Эти инструкции выполняют либо AND, либо NAND, а затем устанавливают целевую операционную маску на основе значений результата, равных нулю или ненулевых. Обратите внимание, что, как и инструкции сравнения, они принимают два регистра opmask, один как адресат, а другой — обычную opmask.

Инструкция Набор удлинителей Описание VPTESTMD , VPTESTMQ F Логическое И и установка маски для 32- или 64-битных целых чисел. VPTESTNMD , VPTESTNMQ F Логическая И-НЕ и маска для 32- или 64-битных целых чисел. VPTESTMB , VPTESTMW BW Логическое И и установка маски для 8- или 16-битных целых чисел. VPTESTNMB , VPTESTNMW BW Логическая И-НЕ и маска для 8- или 16-битных целых чисел. Сжать и развернуть [ править ]

Инструкции сжатия и развертывания соответствуют одноименным операциям APL . Они используют операционную маску немного иначе, чем другие инструкции AVX-512. Сжатие сохраняет только значения, отмеченные в маске, но сохраняет их сжатыми, пропуская и не резервируя место для немаркированных значений. Expand работает противоположным образом, загружая столько значений, сколько указано в маске, а затем распределяя их по выбранным позициям.

Переставить [ править ]

Добавлен новый набор инструкций перестановки для полных перестановок двух входов. Все они принимают три аргумента, два исходных регистра и один индекс; результат выводится путем перезаписи либо первого исходного регистра, либо индексного регистра. AVX-512BW расширяет инструкции, включая также 16-битные (слово) версии, а расширение AVX-512_VBMI определяет байтовые версии инструкций.

Инструкция Набор удлинителей Описание VPERMB VBMI Переставить упакованные байтовые элементы. VPERMW BW Перестановка элементов упакованных слов. VPERMT2B VBMI Перестановка полного байта перезаписывает первый источник. VPERMT2W BW Полная перестановка слов перезаписывает первый источник. VPERMI2PD , VPERMI2PS F Полная перестановка с одинарной / двойной плавающей запятой, перезаписывающая индекс. VPERMI2D , VPERMI2Q F Полная перестановка двойного слова / четверного слова, перезаписывающая индекс. VPERMI2B VBMI Перестановка полного байта перезаписывает индекс. VPERMI2W BW Полная перестановка слов перезаписывает индекс. VPERMT2PS , VPERMT2PD F Полная перестановка с одинарной / двойной плавающей запятой, перезапись первого источника. VPERMT2D , VPERMT2Q F Полная перестановка двойного слова / четверного слова, перезаписывающая первый источник. VSHUFF32x4 , VSHUFF64x2 , Побитовая троичная логика [ править ]

Две новые добавленные инструкции могут логически реализовать все возможные побитовые операции между тремя входами. В качестве входных данных они принимают три регистра и 8-битное непосредственное поле. Каждый бит на выходе генерируется с помощью поиска трех соответствующих битов на входах, чтобы выбрать одну из 8 позиций в 8-битном немедленном. Поскольку с использованием трех битов возможны только 8 комбинаций, это позволяет выполнять все возможные 3 входные побитовые операции. [6] Это единственные побитовые векторные инструкции в AVX-512F; Версии EVEX двух исходных команд побитовых векторов SSE и AVX AND, ANDN, OR и XOR были добавлены в AVX-512DQ.

Разница между версиями двойного слова и четверного слова заключается только в применении opmask.

Инструкция Описание VPTERNLOGD , VPTERNLOGQ Побитовая тернарная логика A0 A1 A2 Двойное И (0x80) Двойное ИЛИ (0xFE) Побитовое смешение (0xCA) 0 0 0 0 0 0 0 0 1 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 1 1 1 1 1 1 Конверсии [ править ]

Был добавлен ряд инструкций по преобразованию или перемещению; они завершают набор инструкций по преобразованию, доступных в SSE2.

VPMOVQD , VPMOVSQD , VPMOVUSQD ,

VPMOVQW , VPMOVSQW , VPMOVUSQW ,

VPMOVQB , VPMOVSQB , VPMOVUSQB ,

VPMOVDW , VPMOVSDW , VPMOVUSDW ,

VPMOVDB , VPMOVSDB , VPMOVUSDBVCVTPS2UQQ , VCVTPD2UQQ ,

VCVTTPS2QQ , VCVTTPD2QQ ,

VCVTTPS2UQQ , VCVTTPD2UQQРазложение с плавающей запятой [ править ]

Среди уникальных новых функций AVX-512F — инструкции для декомпозиции значений с плавающей запятой и обработки специальных значений с плавающей запятой . Поскольку эти методы совершенно новые, они также существуют в скалярных версиях.

Инструкция Описание VGETEXPPD , VGETEXPPS Преобразование показателей упакованных значений fp в значения fp VGETEXPSD , VGETEXPSS Преобразование показателя скалярного значения fp в значение fp VGETMANTPD , VGETMANTPS Извлечь вектор нормализованных мантисс из вектора float32 / float64 VGETMANTSD , VGETMANTSS Извлечь float32 / float64 нормализованной мантиссы из скаляра float32 / float64 VFIXUPIMMPD , VFIXUPIMMPS Исправить специальные упакованные значения float32 / float64 VFIXUPIMMSD , VFIXUPIMMSS Исправить специальное скалярное значение float32 / float64 Арифметика с плавающей запятой [ править ]

Это второй набор новых методов с плавающей запятой, который включает в себя новое масштабирование и приближенное вычисление обратной и обратной величины квадратного корня. Приблизительные взаимные инструкции гарантируют, что относительная ошибка не превышает 2 -14 . [6]

Инструкция Описание VRCP14PD , VRCP14PS Вычислить приблизительные обратные значения упакованных значений float32 / float64 VRCP14SD , VRCP14SS Вычислить приблизительные обратные значения скалярного значения float32 / float64 VRNDSCALEPS , VRNDSCALEPD Округлить упакованные значения float32 / float64, чтобы включить заданное количество дробных бит VRNDSCALESS , VRNDSCALESD Круглое скалярное значение float32 / float64 для включения заданного количества дробных битов VRSQRT14PD , VRSQRT14PS Вычислить приблизительные значения, обратные квадратным корням упакованных значений float32 / float64 VRSQRT14SD , VRSQRT14SS Вычислить приблизительную величину, обратную квадратному корню из скалярного значения float32 / float64 VSCALEFPS , VSCALEFPD Масштабирование упакованных значений float32 / float64 со значениями float32 / float64 VSCALEFSS , VSCALEFSD Масштабировать скалярное значение float32 / float64 с помощью значения float32 / float64 Трансляция [ править ]

Инструкция Набор удлинителей Описание VBROADCASTSS , VBROADCASTSD F, VL Трансляция одинарного / двойного значения с плавающей точкой VPBROADCASTB , VPBROADCASTW ,

VPBROADCASTD , VPBROADCASTQF, VL, DQ, BW Передача целочисленного значения байта / слова / двойного слова / четверного слова VBROADCASTI32X2 ,

VBROADCASTI64X2 , VBROADCASTI32X4 ,

VBROADCASTI32X8 , VBROADCASTI64X4F, VL, DQ, BW Передача двух или четырех целочисленных значений двойного / четверного слова Разное [ править ]

Инструкция Набор удлинителей Описание VALIGND , VALIGNQ F, VL Выравнивание векторов двойных или четверных слов VDBPSADBW BW Двойная блочная упакованная сумма абсолютных разностей (SAD) в беззнаковых байтах VPABSQ F Упакованное четверное слово абсолютного значения VPMAXSQ , VPMAXUQ F Максимум упакованного четверного слова со знаком / без знака VPMINSQ , VPMINUQ F Минимум упакованного четверного слова со знаком / без знака VPROLD , VPROLVD ,

VPROLQ , VPROLVQ ,

VPRORD , VPRORVD ,

VPRORQ , VPRORVQF Бит повернуть влево или вправо VPSCATTERDD , VPSCATTERDQ ,

VPSCATTERQD , VPSCATTERQQF Скаттер-упакованное двойное слово / четверное слово с индексами двойного слова и четверного слова со знаком VSCATTERDPS , VSCATTERDPD ,

VSCATTERQPS , VSCATTERQPDF Скаттер упакованный float32 / float64 с индексами двойного слова и четверного слова со знаком Новые инструкции по наборам [ править ]

Обнаружение конфликтов [ править ]

Инструкции в обнаружении конфликтов AVX-512 (AVX-512CD) предназначены для помощи в эффективном вычислении бесконфликтных подмножеств элементов в циклах, которые обычно невозможно безопасно векторизовать. [8]

Инструкция Имя Описание VPCONFLICTD , VPCONFLICTQ Обнаружение конфликтов в векторе упакованных значений двойных или четверных слов. Сравнивает каждый элемент в первом источнике со всеми элементами на том же или более раннем месте во втором источнике и формирует битовый вектор результатов. VPLZCNTD , VPLZCNTQ Подсчитайте количество начальных нулевых битов для упакованных значений двойного или четверного слова. Векторизованная LZCNT инструкция. VPBROADCASTMB2Q , VPBROADCASTMW2D Передать маску в векторный регистр. Либо 8-битная маска для вектора четверного слова, либо 16-битная маска для вектора двойного слова. Экспоненциальная и обратная [ править ]

Экспоненциальные и обратные инструкции AVX-512 содержат более точные приблизительные обратные инструкции, чем в основе AVX-512; относительная погрешность не превышает 2 −28 . Они также содержат две новые экспоненциальные функции с относительной ошибкой не более 2 −23 . [6]

Инструкция Описание VEXP2PD , VEXP2PS Вычислить примерную экспоненту 2 ^ x упакованных значений с плавающей запятой одинарной или двойной точности VRCP28PD , VRCP28PS Вычисление приблизительных обратных величин упакованных значений с плавающей запятой одинарной или двойной точности VRCP28SD , VRCP28SS Вычислить приблизительное значение, обратное скалярному значению с плавающей запятой одиночной или двойной точности VRSQRT28PD , VRSQRT28PS Вычисление приблизительных обратных величин квадратных корней упакованных значений с плавающей запятой одинарной или двойной точности VRSQRT28SD , VRSQRT28SS Вычислить приблизительную величину, обратную квадратному корню из скалярного значения с плавающей запятой одинарной или двойной точности Предварительная выборка [ править ]

Инструкции предварительной выборки AVX-512 содержат новые операции предварительной выборки для новых функций разброса и сбора, представленных в AVX2 и AVX-512. T0 Предварительная выборка означает предварительную выборку в кэш уровня 1 и T1 означает предварительную выборку в кеш уровня 2.

Инструкция Описание VGATHERPF0DPS , VGATHERPF0QPS , VGATHERPF0DPD , VGATHERPF0QPD Используя подписанные индексы dword / qword, выполните предварительную выборку разреженных участков памяти байтов, содержащих данные с одинарной / двойной точностью, используя opmask k1 и подсказку T0. VGATHERPF1DPS , VGATHERPF1QPS , VGATHERPF1DPD , VGATHERPF1QPD Используя подписанные индексы dword / qword, выполните предварительную выборку разреженных участков памяти байтов, содержащих данные с одинарной / двойной точностью, используя opmask k1 и подсказку T1. VSCATTERPF0DPS , VSCATTERPF0QPS , VSCATTERPF0DPD , VSCATTERPF0QPD Используя подписанные индексы dword / qword, выполните предварительную выборку разреженных ячеек памяти байтов, содержащих данные с одинарной / двойной точностью, используя маску записи k1 и подсказку T0 с намерением записи. VSCATTERPF1DPS , VSCATTERPF1QPS , VSCATTERPF1DPD , VSCATTERPF1QPD Используя подписанные индексы dword / qword, предварительно выберите ячейки памяти с разреженными байтами, содержащие данные с одинарной / двойной точностью, используя маску записи k1 и подсказку T1 с намерением записи. 4FMAPS и 4VNNIW [ править ]

Инструкция Набор удлинителей Описание V4FMADDPS , V4FMADDSS 4 кадра Упакованное / скалярное объединенное умножение с плавающей запятой одинарной точности с плавающей запятой (4 итерации) V4FNMADDPS , V4FNMADDSS 4 кадра Упакованные / скалярные числа с плавающей запятой одинарной точности, объединенные умножением-сложением и отрицанием (4 итерации) VP4DPWSSD 4VNNIW Точечный продукт слов со знаком с накоплением двойных слов (4 итерации) VP4DPWSSDS 4VNNIW Точечный продукт слов со знаком с накоплением двойных слов и насыщением (4-итерации) BW, DQ и VBMI [ править ]

AVX-512DQ добавляет новые инструкции двойного и четверного слова. AVX-512BW добавляет байтовые и словарные версии тех же инструкций и добавляет байтовые и словные версии инструкций двойного / четверного слова в AVX-512F. Несколько инструкций , которые получают только словоформы с AVX-512BW приобретает байтовую форму с расширением AVX-512_VBMI ( VPERMB , VPERMI2B , VPERMT2B , VPMULTISHIFTQB ).

К набору инструкций маски были добавлены две новые инструкции: KADD и KTEST (формы B и W с AVX-512DQ, D и Q с AVX-512BW). Остальные инструкции маски, которые имели только словоформы, получили байтовые формы с AVX-512DQ и формы двойного / четверного слова с AVX-512BW. KUNPCKBW был продлен до KUNPCKWD и KUNPCKDQ от AVX-512BW.

Среди инструкций, добавленных AVX-512DQ, есть несколько инструкций SSE, AVX, которые не получили версии AVX-512 с AVX-512F, среди них все две входные побитовые инструкции и целочисленные инструкции извлечения / вставки.

Ниже приведены полностью новые инструкции.

Инструкции с плавающей точкой [ править ]

Введены три новые операции с плавающей запятой. Поскольку они являются новинкой не только для AVX-512, у них есть как упакованные / SIMD, так и скалярные версии.

Эти VFPCLASS инструкции проверяют , является ли значение с плавающей точкой является одним из значений с плавающей запятой восемь специальных, какой из восьми значений вызовет бит в регистре маски выходной управляются непосредственной областью. В VRANGE инструкции выполняет минимальные или максимальные операции в зависимости от значения непосредственного поля, которое также может контролировать , если операция выполняется абсолютной или нет , и отдельно , как обрабатываются знак. Эти VREDUCE команды действуют на одном источнике, и вычесть из этого целой части величины исходного плюса числа бит , указанных в непосредственном поле его фракции.

Инструкция Набор удлинителей Описание VFPCLASSPS , VFPCLASSPD DQ Типы тестирования упакованных значений с плавающей запятой одинарной и двойной точности. VFPCLASSSS , VFPCLASSSD DQ Типы тестов скалярных значений с плавающей запятой одинарной и двойной точности. VRANGEPS , VRANGEPD DQ Расчет ограничения диапазона для упакованных значений с плавающей запятой. VRANGESS , VRANGESD DQ Расчет ограничения диапазона для скалярных значений с плавающей запятой. VREDUCEPS , VREDUCEPD DQ Выполните преобразование сокращения для упакованных значений с плавающей запятой. VREDUCESS , VREDUCESD DQ Выполните преобразование сокращения для скалярных значений с плавающей запятой. Другие инструкции [ править ]

Инструкция Набор удлинителей Описание VPMOVM2D , VPMOVM2Q DQ Преобразуйте регистр маски в векторный регистр с двойным или четверным словом. VPMOVM2B , VPMOVM2W BW Преобразуйте регистр маски в регистр вектора байта или слова. VPMOVD2M , VPMOVQ2M DQ Преобразуйте регистр вектора двойного или четвертого слова в регистр маски. VPMOVB2M , VPMOVW2M BW Преобразуйте регистр вектора байта или слова в регистр маски. VPMULLQ DQ Множественно упакованные четверные слова сохраняют низкий результат. Четырехсловная версия VPMULLD. VBMI2 [ править ]

Расширьте возможности VPCOMPRESS и VPEXPAND за счет вариантов байтов и слов. Инструкции по смене новые.

Инструкция Описание VPCOMPRESSB , VPCOMPRESSW Сохранение разреженных упакованных целочисленных значений байтов / слов в плотную память / регистр VPEXPANDB , VPEXPANDW Загрузка разреженных упакованных целочисленных значений байтов / слов из плотной памяти / регистра VPSHLD Объединить и сдвинуть упакованные данные влево VPSHLDV Объединение и переменный сдвиг упакованных данных влево VPSHRD Объединение и сдвиг упакованных данных вправо логически VPSHRDV Объединение и переменный сдвиг упакованных данных вправо логический ВННИ [ править ]

Инструкции векторной нейронной сети.

Инструкция Описание VPDPBUSD Умножение и сложение байтов без знака и со знаком VPDPBUSDS Умножайте и складывайте беззнаковые и подписанные байты с насыщением VPDPWSSD Умножение и складывание целых слов со знаком VPDPWSSDS Умножайте и складывайте целые числа слова с насыщенностью IFMA [ править ]

Инструкция Набор удлинителей Описание VPMADD52LUQ IFMA Упакованное умножение беззнаковых 52-битных целых чисел и добавление младших 52-битных произведений к сумматорам qword VPMADD52HUQ IFMA Упакованное умножение беззнаковых 52-битных целых чисел и добавление старших 52-битных произведений к 64-битным аккумуляторам VPOPCNTDQ и BITALG [ править ]

Инструкция Набор удлинителей Описание VPOPCNTD , VPOPCNTQ VPOPCNTDQ Возвращает количество бит, установленное на 1 в двойном слове / четвертом слове VPOPCNTB , VPOPCNTW BITALG Возвращает количество бит, установленное на 1 в байтах / словах VPSHUFBITQMB BITALG Перемешать биты из элементов четверного слова, используя байтовые индексы, в маску VP2INTERSECT [ править ]

Инструкция Набор удлинителей Описание VP2INTERSECTD , VP2INTERSECTQ VP2INTERSECT Вычислить пересечение двойных слов / четверных слов, чтобы пара регистров маски

GFNI [ править ]

Новые инструкции для поля Галуа в кодировке EVEX :

Инструкция Описание VGF2P8AFFINEINVQB Обратное аффинное преобразование поля Галуа VGF2P8AFFINEQB Аффинное преобразование поля Галуа VGF2P8MULB Поле Галуа умножение байтов VPCLMULQDQ [ править ]

VPCLMULQDQ с AVX-512F добавляет 512-битную версию инструкции PCLMULQDQ в кодировке EVEX. В AVX-512VL добавлены 256- и 128-битные версии с кодировкой EVEX. Только VPCLMULQDQ (то есть на процессорах, отличных от AVX512) добавляет только 256-битную версию с кодировкой VEX. (Доступность 128-битной версии с кодировкой VEX обозначается разными битами CPUID: PCLMULQDQ и AVX.) Более широкие, чем 128-битные варианты инструкции выполняют одну и ту же операцию с каждой 128-битной частью входных регистров, но они это делают. не расширять его, чтобы выбрать четверные слова из разных 128-битных полей (значение операнда imm8 одинаково: выбирается либо младшее, либо старшее четверное слово из 128-битного поля).

Инструкция Описание VPCLMULQDQ Четверное слово умножения без переноса VAES [ править ]

Команды AES в кодировке VEX и EVEX . Более широкие, чем 128-битные варианты инструкции, выполняют одну и ту же операцию с каждой 128-битной частью входных регистров. Версии VEX можно использовать без поддержки AVX-512.

Инструкция Описание VAESDEC Выполните один раунд потока дешифрования AES VAESDECLAST Выполнить последний раунд потока дешифрования AES VAESENC Выполните один раунд потока шифрования AES VAESENCLAST Выполните последний раунд потока шифрования AES BF16 [ править ]

Инструкции по ускорению AI, работающие в формате Bfloat16 .

Инструкция Описание VCVTNE2PS2BF16 Преобразование двух упакованных чисел одинарной точности в одно упакованное число Bfloat16 VCVTNEPS2BF16 Преобразование одного упакованного числа одинарной точности в одно упакованное число Bfloat16 VDPBF16PS Вычислить скалярное произведение двух пар Bfloat16 и собрать результат в одно упакованное число одинарной точности. Устаревшие инструкции обновлены версиями в кодировке EVEX [ править ]

Устаревшая кодировка Группа инструкции Расширения AVX-512 SSE

SSE2

MMXAVX

SSE3

SSE4.1AVX2

FMAда да Нет VADD VADDPD , VADDPS , VADDSD , VADDSS F, VL ВАНД VANDPD , VANDPS , VANDNPD , VANDNPS VL, DQ VCMP VCMPPD , VCMPPS , VCMPSD , VCMPSS F VCOM VCOMISD , VCOMISS F VDIV VDIVPD , VDIVPS , VDIVSD , VDIVSS F, VL VCVT VCVTDQ2PD , VCVTDQ2PS , VCVTPD2DQ , VCVTPD2PS , VCVTPH2PS , VCVTPS2PH , VCVTPS2DQ , VCVTPS2PD ,

VCVTSD2SI , VCVTSD2SS , VCVTSI2SD , VCVTSI2SS , VCVTSS2SD , VCVTSS2SI ,

VCVTTPD2DQ , VCVTTPS2DQ , VCVTTSD2SI , VCVTTSS2SIVMOVDDUP ,

VMOVHLPS , VMOVHPD , VMOVHPS , VMOVLHPS , VMOVLPD , VMOVLPS ,

VMOVNTDQA , VMOVNTDQ , VMOVNTPD , VMOVNTPS ,

VMOVSD , VMOVSHDUP , VMOVSLDUP , VMOVSS , VMOVUPD , VMOVUPS VMOVDQA32 , VMOVDQA64 ,

VMOVDQU8 , VMOVDQU16 , VMOVDQU32 , VMOVDQU64VPADDSB , VPADDSW , VPADDUSB , VPADDUSW

VPMOVZXBW , VPMOVZXBD , VPMOVZXBQ , VPMOVZXWD , VPMOVZXWQ , VPMOVZXDQ

VPUNPCKLBW , VPUNPCKLWD , VPUNPCKLDQ , VPUNPCKLQDQ

VPSLLDQ , VPSLLW , VPSLLD , VPSLLQ ,

VPSRAW , VPSRAD , VPSRAQ ,

VPSRLDQ , VPSRLW , VPSRLD , VPSRLQ ,

VPSLLVW , VPSLLVD , VPSLLVQ ,

VPSRLVW , VPSRLVD , VPSRLVQ ,

VPSHUFPD , VPSHUFPSVEXTRACTI32X4 , VEXTRACTI64X2 , VEXTRACTI32X8 , VEXTRACTI64X4

VINSERTI32X4 , VINSERTI64X2 , VINSERTI32X8 , VINSERTI64X4

VFMADD132PS , VFMADD213PS , VFMADD231PS ,

VFMADD132SD , VFMADD213SD , VFMADD231SD ,

VFMADD132SS , VFMADD213SS , VFMADD231SSVFMADDSUB132PS , VFMADDSUB213PS , VFMADDSUB231PS

VFMSUBADD132PS , VFMSUBADD213PS , VFMSUBADD231PS

VFMSUB132PS , VFMSUB213PS , VFMSUB231PS ,

VFMSUB132SD , VFMSUB213SD , VFMSUB231SD ,

VFMSUB132SS , VFMSUB213SS , VFMSUB231SSVFNMADD132PS , VFNMADD213PS , VFNMADD231PS ,

VFNMADD132SD , VFNMADD213SD , VFNMADD231SD ,

VFNMADD132SS , VFNMADD213SS , VFNMADD231SSVFNMSUB132PS , VFNMSUB213PS , VFNMSUB231PS ,

VFNMSUB132SD , VFNMSUB213SD , VFNMSUB231SD ,

VFNMSUB132SS , VFNMSUB213SS , VFNMSUB231SSПроцессоры с AVX-512 [ править ]

- Intel

- Приземление рыцарей (Xeon Phi x200): [1] [9] AVX-512 F, CD, ER, PF

- Knights Mill (Xeon Phi x205): [7] AVX-512 F, CD, ER, PF, 4FMAPS, 4VNNIW, VPOPCNTDQ

- Skylake-SP , Skylake-X : [10] [11] [12] AVX-512 F, CD, VL, DQ, BW

- Cannon Lake : [7] AVX-512 F, CD, VL, DQ, BW, IFMA, VBMI.

- Каскадное озеро : AVX-512 F, CD, VL, DQ, BW, VNNI

- Озеро Купер : AVX-512 F, CD, VL, DQ, BW, VNNI, BF16

- Ледяное озеро , [7] Ракетное озеро : [13] AVX-512 F, CD, VL, DQ, BW, IFMA, VBMI, VBMI2, VPOPCNTDQ, BITALG, VNNI, VPCLMULQDQ, GFNI, VAES

- Tiger Lake (кроме Pentium и Celeron [14] ): [15] AVX512 F, CD, VL, BW, DQ, VBMI, IFMA, VBMI2, VPOPCNTDQ, BITALG, VNNI, VPCLMULQDQ, GFNI, VAES, VP2INTERSECT

- Ядро «CNS» (8c / 8t, AVX512F / CD / VL / BW / DQ / IFMA / VBMI) [16] [17]

Подмножество AVX-512 F CD ER ПФ 4 кадра 4VNNIW VPOPCNTDQ VL DQ BW IFMA VBMI ВННИ BF16 VBMI2 BITALG VPCLMULQDQ GFNI VAES VP2INTERSECT Процессоры Knights Landing (Xeon Phi x200) (2016 г.) да да Нет Процессоры Knights Mill (Xeon Phi x205) (2017 г.) да да Нет Skylake-SP , процессоры Skylake-X (2017) Нет Нет Нет да Нет Процессоры Cannon Lake (2018) да Нет Процессоры Cascade Lake (2019) Нет да Нет Процессоры Cooper Lake (2020 г.) да Нет Процессоры Ice Lake (2019) да да Нет да Нет Процессоры Tiger Lake (2020 г.) да Процессоры Rocket Lake (2021 г.) Нет QEMU поддерживает эмуляцию AVX-512 в своем TCG.

Производительность [ править ]

Советник Intel «Vectorization» (начиная с версии 2016 Update 3) поддерживает исходную производительность AVX-512 и анализ качества векторного кода для процессора Intel Xeon Phi 2-го поколения (кодовое название Knights Landing ). Наряду с традиционным профилем горячих точек, рекомендациями советников и «бесшовной» интеграцией диагностики векторизации Intel Compiler, анализ Advisor Survey также предоставляет метрики AVX-512 ISA и новые специфичные для AVX-512 «характеристики», например разброс, сжатие / расширение, использование маски. [18] [19]

Основная статья: Расширенные векторные расширения § Понижение частоты

На некоторых процессорах инструкции AVX-512 вызывают даже большее снижение частоты, чем его предшественники, что приводит к штрафу за смешанные рабочие нагрузки. Дополнительное понижение частоты запускается 512-битной шириной векторов и зависит от характера выполняемых инструкций, а использование 128- или 256-битной части AVX-512 (AVX-512VL) не запускает его. В результате gcc и clang по умолчанию предпочитают использовать 256-битные векторы. [20]

См. Также [ править ]

- Набор инструкций FMA (FMA)

- Набор команд XOP (XOP)

- Scalable Vector Extension for ARM — новый набор векторных команд (дополняющий VFP и NEON ), поддерживающий очень широкую разрядность и единый двоичный код, который может автоматически адаптироваться к максимальной ширине, поддерживаемой оборудованием.

Ссылки [ править ]

- ^ a b c d e f Джеймс Рейндерс (23 июля 2013 г.). «Инструкции AVX-512» . Intel . Проверено 20 августа 2013 года .

- ^ «Расширенный интеллект для решений с высокой плотностью кромок» . Intel . Intel . Проверено 8 февраля 2018 .

- ^ a b c Джеймс Рейндерс (17 июля 2014 г.). «Дополнительные инструкции AVX-512» . Intel . Проверено 3 августа 2014 .

- ↑ Антон Шилов. «Процессоры Intel ‘Skylake’ для ПК не поддерживают инструкции AVX-512» . Kitguru.net . Проверено 17 марта 2015 .

- ^ https://lemire.me/blog/2016/10/14/intel-will-add-deep-learning-instructions-to-its-processors/

- ^ a b c d e f g h «Справочник по программированию расширений набора команд архитектуры Intel» (PDF) . Intel . Проверено 29 января 2014 .

- ^ a b c d e f «Справочник по программированию расширений набора команд архитектуры Intel® и будущих функций» . Intel . Проверено 16 октября 2017 .

- ^ «Архитектура AVX-512 / Демиховский плакат» (PDF) . Intel . Проверено 25 февраля 2014 года .

- ^ «Краткое описание процессора Intel® Xeon Phi ™» . Intel . Проверено 12 октября +2016 .

- ^ «Intel представляет платформу серии X: до 18 ядер и 36 потоков, от 242 до 2000 долларов» . Ars Technica . Проверено 30 мая 2017 .

- ^ «Intel® Advanced Vector Extensions 2015/2016: Поддержка в коллекции компиляторов GNU» (PDF) . Gcc.gnu.org . Проверено 20 октября 2016 .

- ^ Патрицио, Энди. «Дорожная карта Intel Xeon для утечек на 2016 год» . Itworld.org . Проверено 20 октября 2016 .

- ^ «Обзор Intel Core i9-11900K — Самый быстрый игровой процессор в мире?» . www.techpowerup.com .

- ^ «Технические характеристики процессора Intel® Celeron® 6305 (4 МБ кэш-памяти, 1,80 ГГц, с IPU)» . ark.intel.com . Проверено 10 ноября 2020 .

- ^ «Использование коллекции компиляторов GNU (GCC): параметры x86» . GNU . Проверено 14 октября 2019 .

- ^ https://centtech.com/ai-technology/

- ^ «x86, x64 Instruction Latency, Memory Latency и CPUID дампы (instlatx64)» . users.atw.hu .

- ^ «Intel® Advisor XE 2016 Обновление 3 Что нового — Программное обеспечение Intel®» . Software.intel.com . Проверено 20 октября 2016 .

- ^ «Советник Intel® — Программное обеспечение Intel®» . Software.intel.com . Проверено 20 октября 2016 .

- ^ Кордес, Питер. «Инструкции SIMD, понижающие частоту процессора» . Переполнение стека .

- MMX (1996)

- 3DNow! (1998)

- SSE (1999)

- SSE2 (2001)

- SSE3 (2004 г.)

- SSSE3 (2006)

- SSE4 (2006 г.)

- SSE5

(2007) - AVX (2008)

- F16C (2009 г.)

- XOP (2009)

- FMA (FMA4: 2011, FMA3: 2012)

- AVX2 (2013 г.)

- AVX-512 (2015 г.)

- ИМТ (ABM: 2007, BMI1: 2012, BMI2: 2013, TBM: 2012)

- ADX (2014 г.)

- SuperH [ необходима ссылка ]

- Большой палец

- MIPS16e ASE

- РВК

- PadLock (2003)

- АЕС-НИ (2008 г.); ARMv8 также имеет инструкции AES

- CLMUL (2010)

- РДРАНД (2012)

- SHA (2013)

- MPX (2015)

- SGX (2015 г.)

- TSX (2013)

- АЧС

- VT-x (2005)

- AMD-V (2006)

- VT-d (AMD-Vi)